## Working Draft American National Standard

# T10 Project 1142D

Revision 20b 13-April-98

## Information technology -SCSI Parallel Interface-2 (SPI-2)

This is a draft proposed American National Standard of Accredited Standards Committee NCITS. As such this is not a completed standard. The T10 Technical Committee may modify this document as a result of comments received during public review and its approval as a standard. Use of the information contained here in is at your own risk.

Permission is granted to members of NCITS, its technical committees, and their associated task groups to reproduce this document for the purposes of NCITS standardization activities without further permission, provided this notice is included. All other rights are reserved. Any commercial or for-profit duplication is strictly prohibited.

T10 Technical Editor:

George O. Penokie IBM MS 2B7 3605 Highway 52 N. Rochester, MN 55901 USA

Telephone: 507-253-5208 Facsimile: 507-253-2880 Email: gop@us.ibm.com

> Reference number ISO/IEC 14776-112 : 199x ANSI NCITS. - 199x

Printed Wednesday, July 22, 1998 2:44 pm

## **POINTS OF CONTACT:**

#### <u>T10 Chair</u>

John B. Lohmeyer Symbios, Inc. 4420 Arrows West Drive Colo Spgs, CO 80907-3444 Tel: (719) 533-7560 Fax: (719) 593-7036 Email: john.lohmeyer@symbios.com

#### NCITS Secretariat

NCITS Secretariat 1250 Eye Street, NW Suite 200 Washington, DC 20005

#### T10 Vice-Chair

Lawrence J. Lamers Adaptec 691 South Milpitas Blvd Milpitus, CA 95035 Tel: (408) 975-7817 Fax: (408) 957-7193 Email: Ijlamers@aol.com

Telephone: 202-737-8888 Facsimile: 202-638-4922 Email: ncits@itic.nw.dc.us

T10 ReflectorInternet address for subscription to the T10 reflector: majordomo@symbios.comThe message body should be: subscribe t10Internet address for distribution via T10 reflector: T10@symbios.com

SCSI Bulletin Board

#### **Document Distribution**

Global Engineering 15 Inverness Way East Englewood, CO 80112-5704 Telephone: 303-792-2181 or 800-854-7179 Facsimile: 303-792-2192

719-533-7950

## ABSTRACT

This standard defines mechanical, electrical, timing requirements, command, and the task management delivery protocol requirements to transfer commands and data between SCSI devices attached to an SCSI parallel interface. This standard is intended to be used in conjunction with the SCSI command sets. The resulting interface facilitates the interconnection of computers and intelligent peripherals and thus provides a common interface standard for both system integrators and suppliers of intelligent peripherals.

## PATENT STATEMENT

**CAUTION:** The developers of this standard have requested that holders of patents that may be required for the implementation of the standard, disclose such patents to the publisher. However, neither the developers nor the publisher have undertaken a patent search in order to identify which, if any, patents may apply to this standard. As of the date of publication of this standard, following calls for the identification of patents that may be required for the implementation of the standard, notice of one or more claims has been received.

By publication of this standard, no position is taken with respect to the validity of this claim or of any rights in connection therewith. The known patent holder has, however, filed a statement of willingness to grant a license under these rights on reasonable and nondiscriminatory terms and conditions to applicants desiring to obtain such a license. Details may be obtained from the publisher.

No further patent search is conducted by the developer or the publisher in respect to any standard it processes. No representation is made or implied that licenses are not required to avoid infringement in the use of this standard.

## Contents

| Page |

|------|

|------|

| 1 Scope                                                         | 1  |

|-----------------------------------------------------------------|----|

| 2 Normative references                                          | 3  |

| 2.1 Approved references                                         |    |

| 2.2 References under development                                |    |

| 2.3 Other references                                            |    |

|                                                                 |    |

| 3 Definitions, symbols, abbreviations, and conventions          | 4  |

| 3.1 Definitions                                                 |    |

| 3.2 Symbols and abbreviations                                   | 8  |

| 3.3 Keywords                                                    | 9  |

| 3.4 Conventions                                                 | 9  |

| 3.5 Notation for Procedures and Functions                       | 10 |

|                                                                 |    |

| 4 General                                                       |    |

| 4.1 Overview                                                    |    |

| 4.1.1 Data transfer modes                                       |    |

| 4.1.2 Cables, Connectors, Signals, Transceivers                 |    |

| 4.1.3 Physical architecture of bus                              |    |

| 4.1.4 Physical topology details and definitions                 |    |

| 4.1.5 Bus loading                                               |    |

| 4.1.6 Termination requirements                                  |    |

| 4.1.7 Device Addressing                                         |    |

| 4.1.8 Protocol                                                  | 15 |

| 5 SCSI parallel interface connectors                            | 10 |

| 5.1 Nonshielded connector                                       |    |

| 5.1.1 Nonshielded connector alternative 1 - A cable             |    |

| 5.1.2 Nonshielded connector alternative 2 - A cable             |    |

| 5.1.3 Nonshielded connector alternative 3 - P cable and Q cable |    |

| 5.1.4 Nonshielded connector alternative 4                       |    |

| 5.2 Shielded connector                                          |    |

| 5.2.1 Shielded connector alternative 1 - A cable                |    |

| 5.2.2 Shielded connector alternative 2 - A cable                |    |

| 5.2.3 Shielded connector alternative 3 - P cable and Q cable    | 25 |

| 5.2.4 Shielded connector alternative 4 - P cable and Q cable    | 25 |

| 5.3 Connector contact assignments                               | 34 |

| 5.3.1 SE assignments                                            | 35 |

| 5.3.2 Differential connector contact assignments                | 39 |

|                                                                 |    |

| 6 SCSI bus interconnect                                         |    |

| 6.1 SCSI bus cables                                             |    |

| 6.2 Interconnect characteristics for signals                    |    |

| 6.3 Decoupling characteristics for TERMPWR and TERMPWRQ lines   |    |

| 6.4 Connection requirements for RESERVED lines                  |    |

| 6.5 Cables used with SE transceivers                            |    |

| 6.5.1 SE ground offset                                          |    |

| 6.6 Cables used with differential transceivers                  |    |

| 6.6.1 HVD stub length and spacing                               |    |

| 6.6.2 LVD stub length and spacing                               | 53 |

| 7 SCSI parallel interface electrical characteristics            | 51 |

| 7.1 SE alternative                                              |    |

| 7.1.1 SE termination                                            |    |

|                                                                 |    |

| 7.1.2 SE output characteristics                              |    |

|--------------------------------------------------------------|----|

| 7.1.3 SE input characteristics                               |    |

| 7.1.4 SE input and output characteristics                    |    |

| 7.2 LVD alternative                                          |    |

| 7.2.1 LVD termination                                        |    |

| 7.2.2 LVD driver characteristics                             |    |

| 7.2.3 LVD receiver characteristics                           |    |

| 7.2.4 LVD capacitive loads                                   |    |

| 7.2.4.1 Management of LVD release glitches                   |    |

| 7.2.5 SE/HVD transmission mode detection                     |    |

| 7.2.5.1 LVD DIFFSENS driver                                  |    |

| 7.2.5.2 LVD DIFFSENS receiver                                |    |

| 7.3 LVD/MSE multimode alternative                            |    |

| 7.3.1 LVD/MSE multimode termination                          |    |

| 7.3.2 LVD/MSE multimode transceiver characteristics          |    |

| 7.3.3 Power for LVD/MSE multimode transceivers               |    |

| 7.3.4 Ground drivers                                         |    |

| 7.4 HVD alternative                                          |    |

| 7.4.1 HVD termination                                        |    |

| 7.4.2 HVD output characteristics                             |    |

| 7.4.3 HVD input characteristics                              |    |

| 7.4.4 SE driver protection                                   |    |

| 7.5 Terminator power                                         | 80 |

|                                                              |    |

| 8 SCSI bus signals                                           |    |

| 8.1 Signal descriptions                                      |    |

| 8.2 Parity checking rules                                    |    |

| 8.3 Signal states                                            |    |

| 8.3.1 SE                                                     |    |

| 8.3.2 Differential                                           |    |

| 8.4 OR-tied signals                                          |    |

| 8.5 Signal sources                                           | 87 |

| 9 SCSI parallel bus timing                                   | 00 |

| 9.1 Timing description                                       |    |

| 9.1.1 Arbitration delay                                      |    |

| 9.1.2 Bus clear delay                                        |    |

| 9.1.2 Bus free delay                                         |    |

| 9.1.5 Bus nee delay                                          |    |

| 9.1.4 Bus settle delay                                       |    |

| 9.1.5 Bus settle delay                                       |    |

| 9.1.7 Data release delay                                     |    |

| 9.1.8 Disconnection delay                                    |    |

| 9.1.9 Power on to selection                                  |    |

| 9.1.10 Receive assertion period                              |    |

| 9.1.10 Receive assertion period                              |    |

| 9.1.12 Receive negation period                               |    |

|                                                              |    |

| 9.1.13 Receive setup time<br>9.1.14 Receive period tolerance |    |

| 9.1.14 Receive period tolerance                              |    |

| 9.1.15 Reset to Selection                                    |    |

| 9.1.16 Reset to Selection                                    |    |

| 9.1.17 Selection abort time                                  |    |

| 9.1.19 Signal Timing Skew                                    |    |

| 9.1.19 Signal Timing Skew                                    |    |

| 9.1.20 System deskew delay                                   |    |

| 9.1.22 Transmit assertion period                             |    |

|                                                              |    |

| 9.1.23 Transmit negation period                                             |     |

|-----------------------------------------------------------------------------|-----|

| 9.1.24 Transmit setup time                                                  |     |

| 9.1.25 Transmit period tolerance                                            | 92  |

| 9.2 Measurement points                                                      |     |

| 9.2.1 SE fast-10 data transfer rates                                        |     |

| 9.2.2 SE fast-20 data transfer rates                                        |     |

| 9.2.3 LVD                                                                   |     |

| 9.2.4 HVD                                                                   |     |

| 9.3 Setup and hold timings                                                  |     |

| 9.3.1 Fast-10 data transfer rates                                           |     |

| 9.3.2 Fast-20 data transfer rates                                           |     |

| 9.3.3 Fast-40 data transfer rates                                           |     |

|                                                                             |     |

| 10 Removal and insertion of SCSI devices                                    |     |

| 10.1 Case 1 - Power-off during removal or insertion                         |     |

| 10.2 Case 2 - RST signal asserted continuously during removal or insertion  |     |

| 10.3 Case 3 - Current I/O processes not allowed during insertion or removal |     |

| 10.4 Case 4 - Current I/O process allowed during insertion or removal       |     |

| · · ·                                                                       |     |

| 11 Logical characteristics                                                  |     |

| 11.1 SCSI bus phases                                                        |     |

| 11.1.1 BUS FREE phase                                                       |     |

| 11.1.1.1 Unexpected bus free                                                |     |

| 11.1.2 ARBITRATION phase                                                    |     |

| 11.1.3 SELECTION phase                                                      |     |

| 11.1.3.1 SELECTION time-out procedure                                       |     |

| 11.1.4 RESELECTION phase                                                    |     |

| 11.1.4.1 RESELECTION                                                        |     |

| 11.1.4.2 RESELECTION time-out procedure                                     |     |

| 11.1.5 Information transfer phases                                          |     |

| 11.1.5.1 Asynchronous information transfer                                  |     |

| 11.1.5.2 Synchronous data transfer                                          |     |

| 11.1.5.3 Wide data transfer                                                 |     |

| 11.1.6 COMMAND phase                                                        |     |

| 11.1.7 Data phase                                                           |     |

| 11.1.7 Data phase                                                           |     |

| 11.1.7.2 DATA IN phase                                                      |     |

|                                                                             |     |

| 11.1.8 STATUS phase                                                         |     |

| 11.1.8.1 STATUS phase exception condition handling                          |     |

| 11.1.9 Message phase                                                        |     |

| 11.1.9.1 MESSAGE IN phase                                                   |     |

| 11.1.9.1.1 MESSAGE IN phase exception condition handling                    |     |

| 11.1.9.2 MESSAGE OUT phase                                                  |     |

| 11.1.9.2.1 MESSAGE OUT phase exception condition handling                   |     |

| 11.1.10 Signal restrictions between phases                                  |     |

| 11.2 SCSI bus conditions                                                    |     |

| 11.2.1 Attention condition                                                  |     |

| 11.2.2 Hard reset                                                           |     |

| 11.2.3 Reset events                                                         |     |

| 11.2.3.1 Transceiver mode change reset event                                |     |

| 11.3 SCSI bus phase sequences                                               |     |

| 11.4 SCSI pointers                                                          |     |

| 11.5 SCSI Interlocked Protocol messages                                     | 117 |

| 11.5.1 Message protocols and formats                                        |     |

| 11.5.1.1 Message protocol rules                                             | 117 |

| 11.5.1.2 Message formats                                                    |     |

| 11.5.1.2.1 One-byte messages                                                |     |

|                                                                             |     |

| 11.5.1.2.2 Two-byte messages1                                    | 18 |

|------------------------------------------------------------------|----|

| 11.5.1.2.3 Extended messages1                                    | 18 |

| 11.5.2 Link control messages                                     |    |

| 11.5.2.1 CONTINUE TASK                                           | 19 |

| 11.5.2.2 DISCONNECT                                              | 20 |

| 11.5.2.3 IDENTIFY                                                | 20 |

| 11.5.2.4 IGNORE WIDE RESIDUE1                                    |    |

| 11.5.2.5 INITIATOR DETECTED ERROR1                               | 22 |

| 11.5.2.6 MESSAGE PARITY ERROR1                                   |    |

| 11.5.2.7 MESSAGE REJECT                                          | 23 |

| 11.5.2.8 MODIFY DATA POINTER1                                    |    |

| 11.5.2.9 NO OPERATION                                            |    |

| 11.5.2.10 RESTORE POINTERS1                                      | 24 |

| 11.5.2.11 SAVE DATA POINTER1                                     |    |

| 11.5.2.12 SYNCHRONOUS DATA TRANSFER REQUEST1                     | 24 |

| 11.5.2.12.1 Target initiated SDTR negotiation1                   |    |

| 11.5.2.12.2 Initiator initiated SDTR negotiation                 |    |

| 11.5.2.13 TARGET TRANSFER DISABLE                                |    |

| 11.5.2.14 TASK COMPLETE                                          |    |

| 11.5.2.15 WIDE DATA TRANSFER REQUEST1                            | 28 |

| 11.5.2.15.1 Target initiated WDTR negotiation1                   | 30 |

| 11.5.2.15.2 Initiator initiated WDTR negotiation1                | 31 |

| 11.5.3 Task attribute messages1                                  | 31 |

| 11.5.3.1 ACA                                                     | 32 |

| 11.5.3.2 HEAD OF QUEUE                                           |    |

| 11.5.3.3 LINKED COMMAND COMPLETE1                                | 33 |

| 11.5.3.4 LINKED COMMAND COMPLETE (WITH FLAG)1                    | 33 |

| 11.5.3.5 ORDERED1                                                |    |

| 11.5.3.6 SIMPLE1                                                 |    |

| 11.5.4 Task management messages1                                 |    |

| 11.5.4.1 ABORT TASK                                              |    |

| 11.5.4.2 ABORT TASK SET1                                         |    |

| 11.5.4.3 CLEAR ACA1                                              |    |

| 11.5.4.4 CLEAR TASK SET1                                         | 35 |

| 11.5.4.5 LOGICAL UNIT RESET1                                     |    |

| 11.5.4.6 TARGET RESET                                            |    |

| 11.5.4.7 TERMINATE TASK1                                         | 36 |

| 11.6 Command processing considerations and exception conditions1 |    |

| 11.6.1 Asynchronous event notification1                          |    |

| 11.6.2 Incorrect initiator connection1                           |    |

| 11.6.3 Unexpected reselection                                    |    |

| 11.7 Use of disconnect-reconnect page parameters                 |    |

| 11.8 SCSI parallel interface services                            |    |

| 11.8.1 Procedure terms                                           |    |

| 11.8.2 Application client SCSI command services                  |    |

| 11.8.2.1 Send SCSI command service                               |    |

| 11.8.3 Device server SCSI command services                       |    |

| 11.8.3.1 Data-in delivery service                                |    |

| 11.8.3.2 Data-out delivery service                               |    |

| 11.8.4 Task management services                                  |    |

| 11.8.4.1.1 ABORT TASK                                            |    |

| 11.8.4.1.2 ABORT TASK                                            |    |

| 11.8.4.1.3 CLEAR ACA                                             |    |

| 11.8.4.1.4 CLEAR TASK SET                                        |    |

| 11.8.4.1.5 LOGICAL UNIT RESET                                    |    |

| 11.8.4.1.6 RESET SERVICE DELIVERY SUBSYSTEM                      |    |

| 11.8.4.1.7 TARGET RESET<br>11.8.4.1.8 TERMINATE TASK<br>11.8.4.1.9 WAKEUP       | 143 |

|---------------------------------------------------------------------------------|-----|

| Annex A Additional requirements for LVD SCSI drivers and receivers              | 144 |

| A.1 System level requirements                                                   | 144 |

| A.2 Driver requirements                                                         |     |

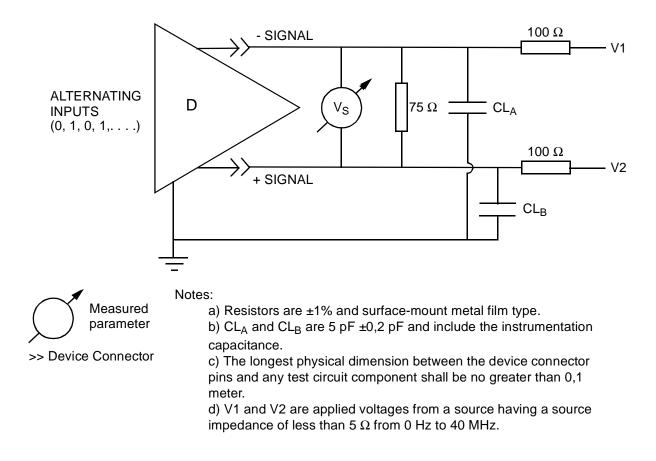

| A.2.1 Differential output voltage, VS                                           |     |

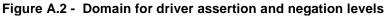

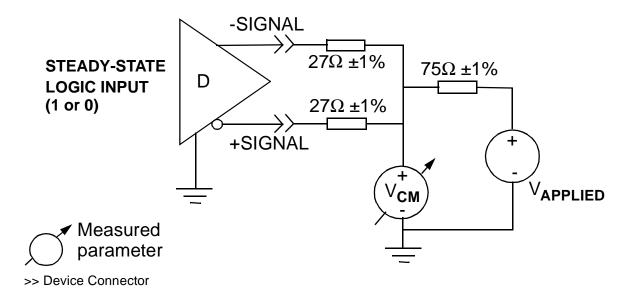

| A.2.2 Offset (common-mode output) voltage, VCM                                  |     |

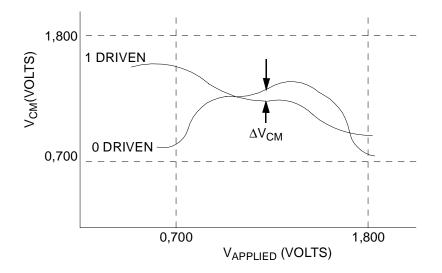

| A.2.3 Short-circuit currents, IO-S and IO+S                                     |     |

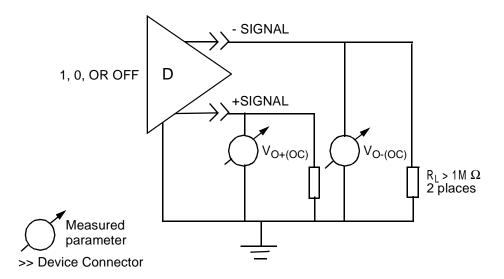

| A.2.4 Open-circuit output voltages, V <sub>O-(OC)</sub> and V <sub>O+(OC)</sub> |     |

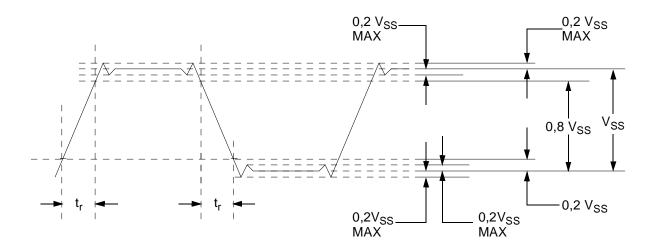

| A.2.5 Output signal waveform                                                    | 150 |

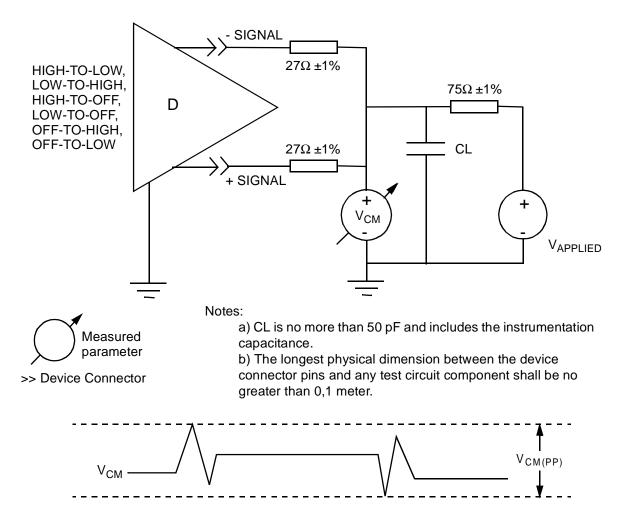

| A.2.6 Dynamic output signal balance, VCM(PP)                                    |     |

| A.3 Receiver characteristics                                                    |     |

| A.3.1 Receiver steady state input voltage requirements                          | 153 |

| A.3.2 Compliance test                                                           |     |

| A.3.3 Receiver setup and hold times                                             |     |

| A.4 Transceiver characteristics                                                 |     |

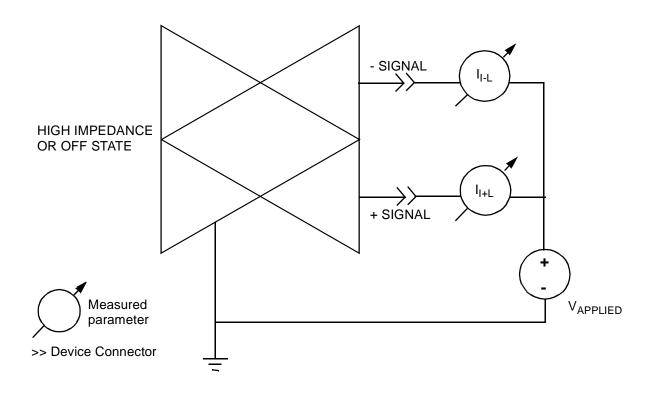

| A.4.1 Transceiver output/input currents, II-L and II+L                          |     |

| A.4.2 Transceiver maximum input voltages                                        | 155 |

| Annex B SCSI configured automatically (SCAM)                                    | 156 |

| B.1 Model                                                                       | 156 |

| B.2 Glossary                                                                    |     |

| B.3 SCAM requirements                                                           |     |

| B.3.1 Configuration requirements                                                |     |

| B.3.2 Timing requirements                                                       |     |

| B.3.2.1 SCAM tolerant power-on to selection delay                               |     |

| B.3.2.2 SCAM tolerant reset to selection delay                                  |     |

| B.3.2.3 SCAM tolerant selection response time                                   |     |

| B.3.2.4 SCAM unassigned ID selection response delay                             |     |

| B.3.2.5 SCAM power-on to SCAM selection delay                                   |     |

| B.3.2.6 SCAM reset to SCAM selection delay                                      |     |

| B.3.2.7 SCAM selection response time                                            |     |

| B.3.2.8 Recommended SCAM selection response time                                |     |

| B.3.2.9 Wide arbitration time                                                   | 158 |

| B.3.3 Device requirements                                                       | 158 |

| B.3.3.1 SCAM tolerant target                                                    |     |

| B.3.3.2 Level 1 SCAM initiator                                                  |     |

| B.3.3.3 Level 1 SCAM target                                                     |     |

| B.3.3.4 Level 2 SCAM initiator                                                  |     |

| B.3.3.5 Level 2 SCAM target                                                     |     |

| B.4 SCAM protocol                                                               |     |

| B.4.1 Initiation                                                                |     |

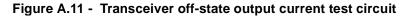

| B.4.1.1 Transfer cycles                                                         |     |

| B.4.1.2 Wired-OR glitch filtering                                               |     |

| B.4.1.3 Isolation stage                                                         |     |

| B.4.1.4 Function sequences                                                      |     |

| B.4.1.4.1 Isolate function                                                      |     |

| B.4.1.4.2 Isolate and set priority flag function                                |     |

| B.4.1.4.3 Configuration process complete function                               |     |

| B.4.1.4.4 Dominant initiator contention function                                |     |

| B.5 SCAM operations                                                             |     |

| B.5.1 SCAM initiator                                                            |     |

| B.5.1.1 Dominant SCAM initiator                                                 | 170 |

| B.5.1.1.1 SCSI ID categorization                                         | 170 |

|--------------------------------------------------------------------------|-----|

| B.5.1.1.2 SCSI ID assignment                                             | 170 |

| B.5.1.2 Subordinate SCAM initiator                                       | 171 |

| B.5.2 Level 1 SCAM target                                                | 171 |

| B.5.3 Level 2 SCAM target                                                | 173 |

| Annex C SCSI bus fairness                                                | 175 |

| C.1 Model                                                                |     |

| C.2 Determining fairness by monitoring prior bus activity                |     |

| C.3 Fairness algorithm                                                   |     |

| C.4 Additional comments                                                  |     |

| Annex D SCA-2 Connector pinouts                                          | 178 |

| D.1 SCA-2 Signal Definitions                                             |     |

| D.1.1 VOLTAGE and GROUND signals                                         |     |

| D.1.2 CHARGE signals                                                     |     |

| D.1.3 SPINDLE SYNC                                                       |     |

| D.1.4 ACTIVE LED OUT                                                     |     |

| D.1.5 Motor Start Controls                                               |     |

| D.1.6 SCSI ID Selection                                                  |     |

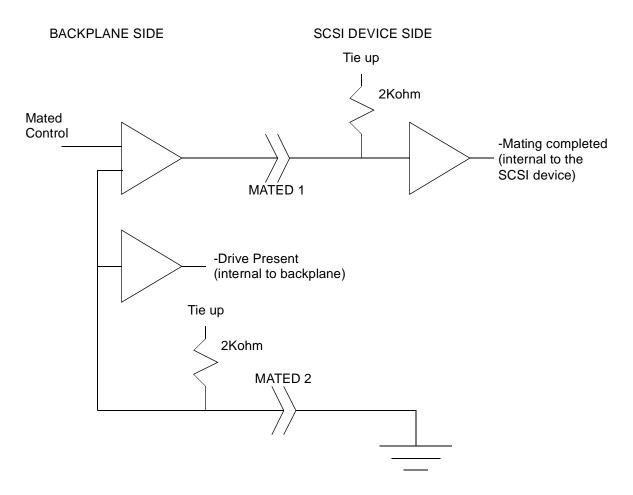

| D.1.7 MATED Signals                                                      |     |

| D.1.7.1 MATED 2/Drive Side                                               |     |

| D.1.7.2 MATED 2/Backplane Side                                           |     |

| D.1.7.3 MATED 1/Drive Side                                               |     |

| D.1.7.4 MATED 1/Backplane Side                                           |     |

| Annex E Interconnecting buses of different widths                        |     |

| Annex F Cabling and cable measurement method recommendations             |     |

| F.1 Cabling                                                              |     |

| F.2 Cable measurement                                                    |     |

| F.2.1 Impedance, TDR, single-ended                                       |     |

| F.2.2 Impedance, TDR, differential                                       |     |

| F.2.3 Attenuation, differential                                          |     |

| F.2.4 Velocity (propagation delay) and skew                              |     |

| F.2.5 D.C. resistance                                                    |     |

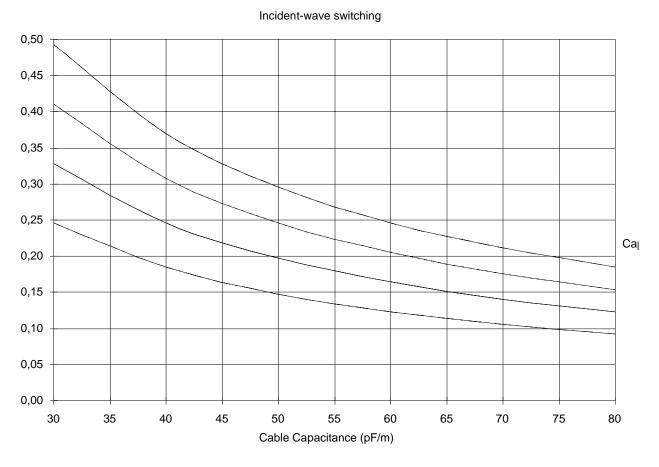

| Annex G Transmission line considerations for fast-20 data transfer rates |     |

| Annex H Measuring SE pin capacitance                                     |     |

| Annex I SCSI ICONS                                                       |     |

| Annex J Example of HVD terminator network                                | 197 |

| Annex K SCSI-3 to SCSI-2 terminology mapping                             |     |

## Tables

| P                                                                                              | age |

|------------------------------------------------------------------------------------------------|-----|

| 1 Transceiver/speed support map                                                                |     |

| 2 Cross-reference to A cable contact assignments                                               |     |

| 3 SE contact assignments - A cable                                                             |     |

| 4 SE contact assignments - P cable                                                             |     |

| 5 · · · · · · · · · · · · · · · · · · ·                                                        |     |

| 5 SE contact assignments - Q cable                                                             |     |

| 6 SE contact assignments - nonshielded alternative 4 connector                                 |     |

| 7 LVD contact assignments - A cable                                                            |     |

| 8 LVD contact assignments - P cable                                                            |     |

| 9 LVD contact assignments - Q cable                                                            |     |

| 10 HVD contact assignments - A cable                                                           |     |

| 11 HVD contact assignments - P cable                                                           |     |

| 12 HVD contact assignments - Q cable                                                           |     |

| 13 HVD and LVD contact assignments - nonshielded alternative 4 connector                       |     |

| 14 Recommended minimum conductor size                                                          |     |

| 15 SE characteristic impedance of cable at maximum indicated data transfer rate                | 48  |

| 16 Differential characteristic impedance of cable at indicated data transfer rate              | 49  |

| 17 SE maximum distance between terminators                                                     | 51  |

| 18 Differential maximum distance between terminators                                           | 52  |

| 20 Minimum stub connection spacing rules for HVD SCSI devices                                  |     |

| 19 HVD stub length and spacing requirements                                                    |     |

| 21 Minimum stub connection spacing rules for LVD SCSI devices                                  |     |

| 22 Electrical input requirements at the device connector                                       |     |

| 23 Input current requirements at the device connector for lines not being driven by the device |     |

| 24 SE steady state output voltage characteristics                                              |     |

| 25 SE input voltage characteristics                                                            |     |

| 26 SE input and output electrical characteristics                                              |     |

| 27 I-V requirements for LVD impedance, common mode impedance, and V <sub>BIAS</sub> tests      |     |

| 28 Values for LVD termination balance test                                                     |     |

|                                                                                                |     |

| 29 Values for LVD capacitive loads                                                             |     |

| 30 Glitch management requirements for devices using LVD drivers                                |     |

| 31 LVD DIFFSENS driver specifications                                                          |     |

| 32 DIFFSENS receiver operating requirements                                                    |     |

| 33 I-V requirements for HVD impedance and common mode impedance tests                          |     |

| 34 Values for HVD termination balance test                                                     |     |

| 35 HVD output voltage characteristics                                                          |     |

| 37 Values for HVD capacitive loads                                                             |     |

| 36 HVD input voltage characteristics                                                           |     |

| 38 Terminator power characteristics at the terminator                                          |     |

| 39 Arbitration priorities by SCSI ID                                                           | 83  |

| 40 Parity checking rules                                                                       | 85  |

| 41 Signal sources                                                                              | 87  |

| 42 SCSI bus timing values                                                                      | 89  |

| 43 Information transfer phases                                                                 |     |

| 44 Wide SCSI byte order                                                                        |     |

| 45 Message format                                                                              |     |

| 46 Extended message format                                                                     |     |

| 47 Link control message codes                                                                  |     |

| 48 IDENTIFY message format                                                                     |     |

| 49 IGNORE WIDE RESIDUE message format                                                          |     |

| 50 IGNORE field definition                                                                     |     |

| 50 IGNORE IIEId delimition                                                                     |     |

| 52 SYNCHRONOUS DATA TRANSFER message format                                                    |     |

| 5                                                                                              |     |

| 53 TRANSFER PERIOD FACTOR field                                                                |     |

| 54 SDTR messages implied agreements                                                            |     |

| 55 WIDE DATA TRANSFER message format                                                           | 128 |

| 56 WDTR messages implied agreements                                                     | 130 |

|-----------------------------------------------------------------------------------------|-----|

| 57 Task attribute message codes                                                         |     |

| 58 ACA message format                                                                   |     |

| 59 HEAD OF QUEUE message format                                                         |     |

| 60 ORDERED message format                                                               |     |

| 61 SIMPLE message format                                                                | 134 |

| 62 Task management message codes                                                        |     |

| 63 DATA TRANSFER DISCONNECT CONTROL                                                     |     |

| 64 SCSI Parallel Interface-2 Standard terms mapped to terms from other SCSI-3 standards | 139 |

| 65 Procedure terms                                                                      | 140 |

| 66 Processing of send SCSI command service procedure                                    | 141 |

| 67 Processing of data-in delivery service procedure                                     |     |

| 68 Processing of data-out delivery service procedure                                    | 142 |

| A.1 System level requirements                                                           |     |

| A.2 Driver steady-state test limits and conditions                                      | 145 |

| A.3 Driver switching test circuit parameters                                            | 151 |

| A.4 Dynamic output balance limits                                                       | 152 |

| A.5 Receiver steady state input voltage ranges                                          | 153 |

| A.6 Receiver minimum and maximum input voltages                                         | 154 |

| B.1 SCAM timing values                                                                  |     |

| B.2 Transfer cycle conditions                                                           | 164 |

| B.3 Identification string                                                               | 165 |

| B.4 Type code                                                                           | 165 |

| B.5 MAXIMUM ID CODE                                                                     | 166 |

| B.6 ID VALID                                                                            | 166 |

| B.7 Function codes                                                                      | 167 |

| B.8 Action codes                                                                        | 168 |

| B.9 Dominance preference code                                                           |     |

| D.1 Voltage specification limits                                                        | 178 |

| D.2 Charge supply to SCSI device                                                        |     |

| D.3 Output characteristics of drive 'ACTIVE LED OUT signal                              | 180 |

| D.4 Definition of motor start controls                                                  |     |

| D.5 Electronic requirements for input controls                                          |     |

| D.6 SCSI device ID selection signals                                                    |     |

| K.1 SPI-2 to SCSI-2 terminology mapping                                                 | 198 |

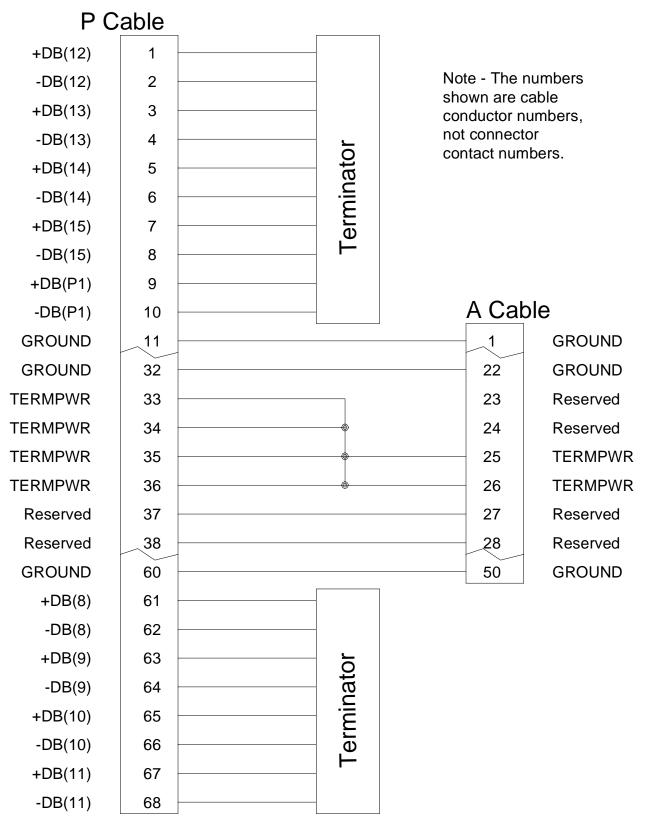

| Figures | 5 |

|---------|---|

|---------|---|

|                                                                                                                                                         | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1 SCSI document road map                                                                                                                                | 2    |

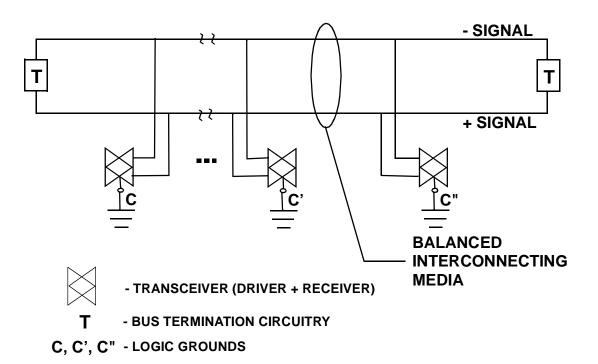

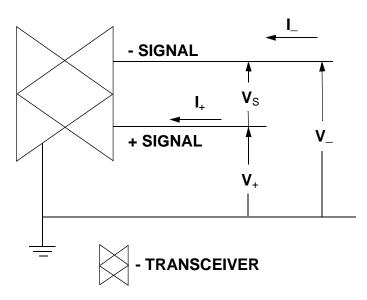

| 2 Differential SCSI bus                                                                                                                                 |      |

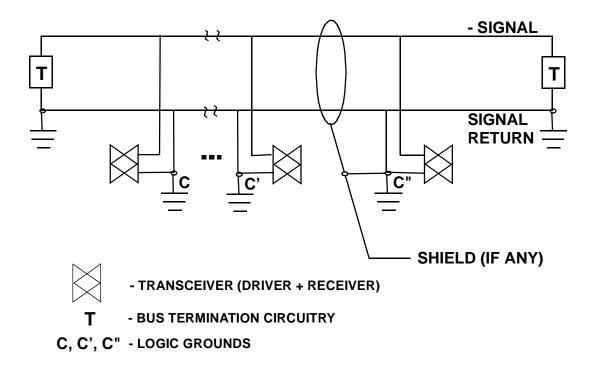

| 3 SE SCSI bus                                                                                                                                           |      |

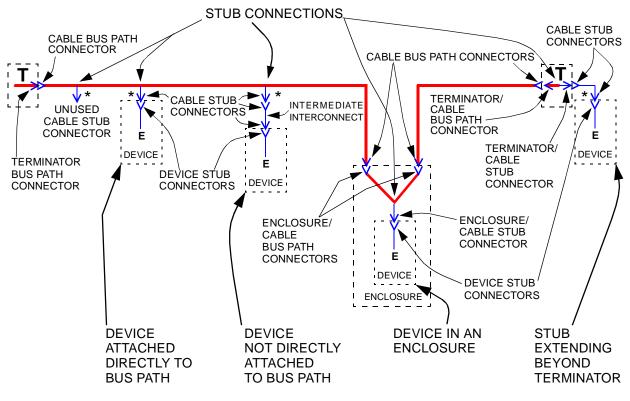

| 4 SCSI bus topology details                                                                                                                             |      |

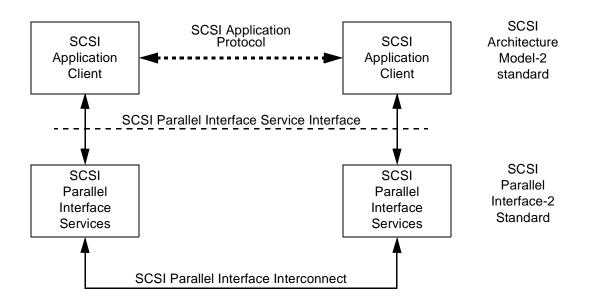

| 5 SCSI Parallel Interface service reference mode                                                                                                        |      |

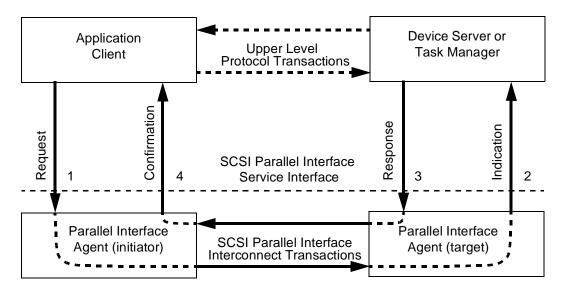

| 6 Model for a four step confirmed services                                                                                                              |      |

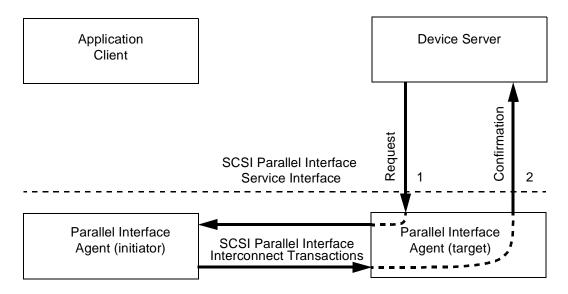

| 7 Model for a two step confirmed services                                                                                                               |      |

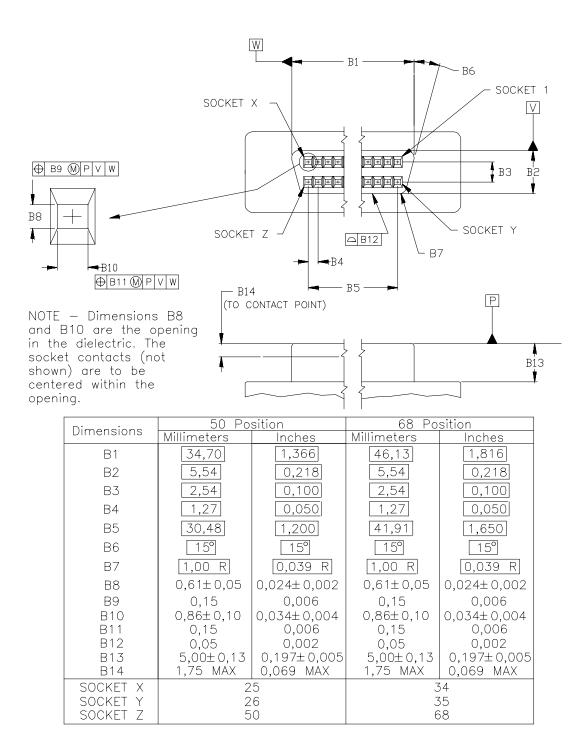

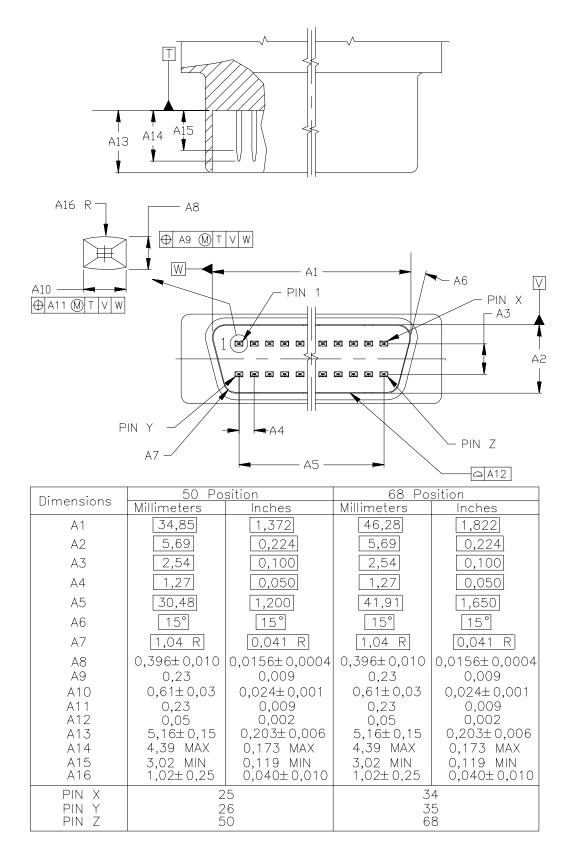

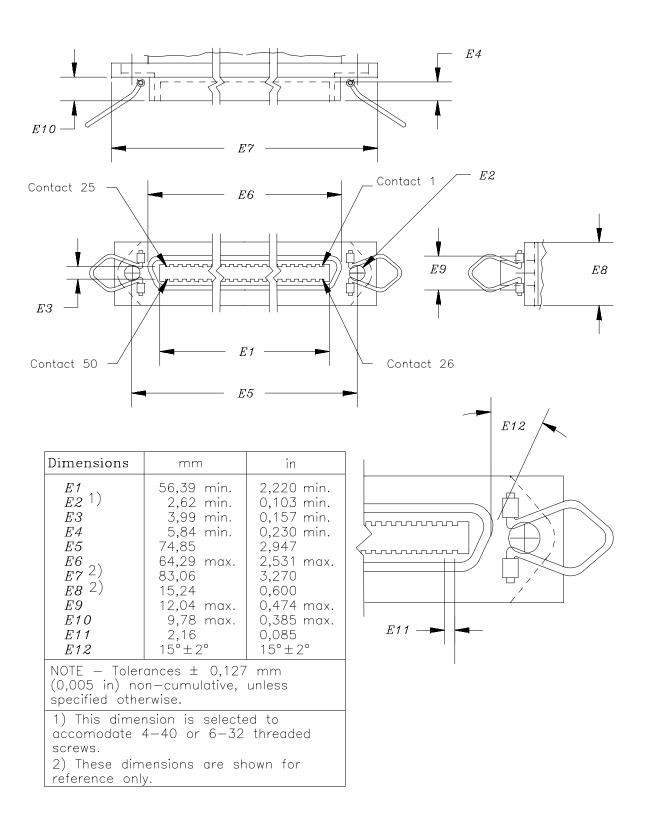

| 8 50/68-contact alternative 1/alternative 3 nonshielded SCSI device connector                                                                           |      |

| 9 50/68-contact alternative 1/alternative 3 nonshielded mating connector                                                                                |      |

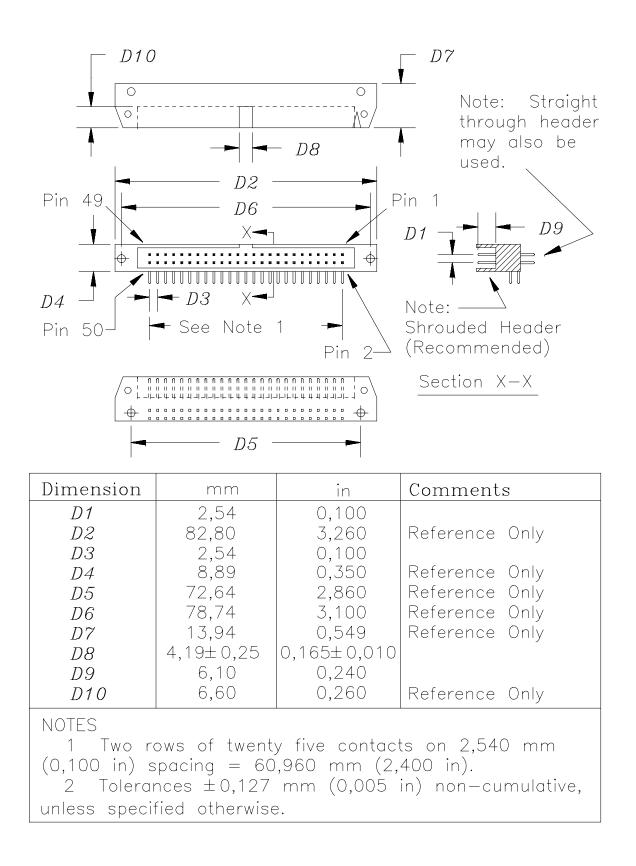

| 10 50-contact alternative 2 nonshielded SCSI device connector (A cable)                                                                                 |      |

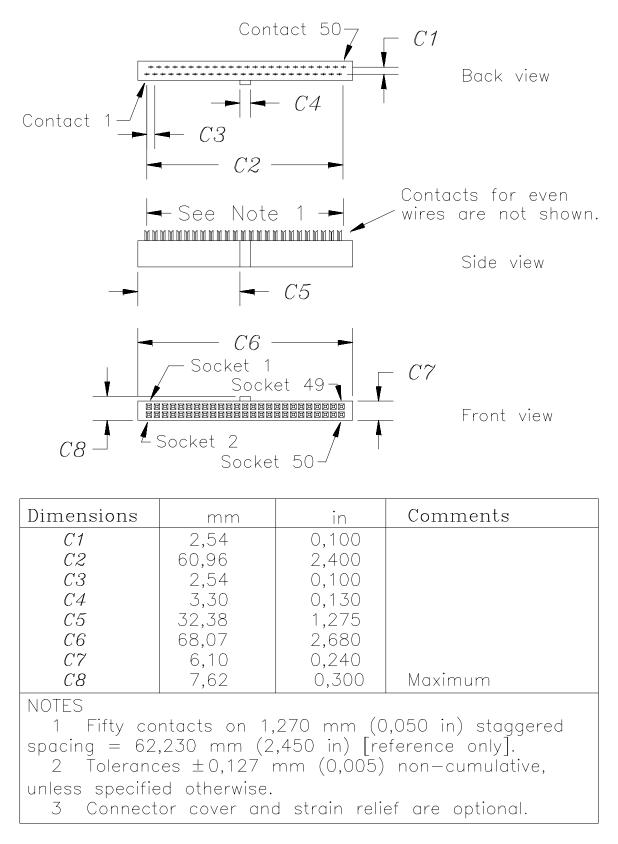

| 11 50-contact alternative 2 nonshielded mating connector (A cable)                                                                                      |      |

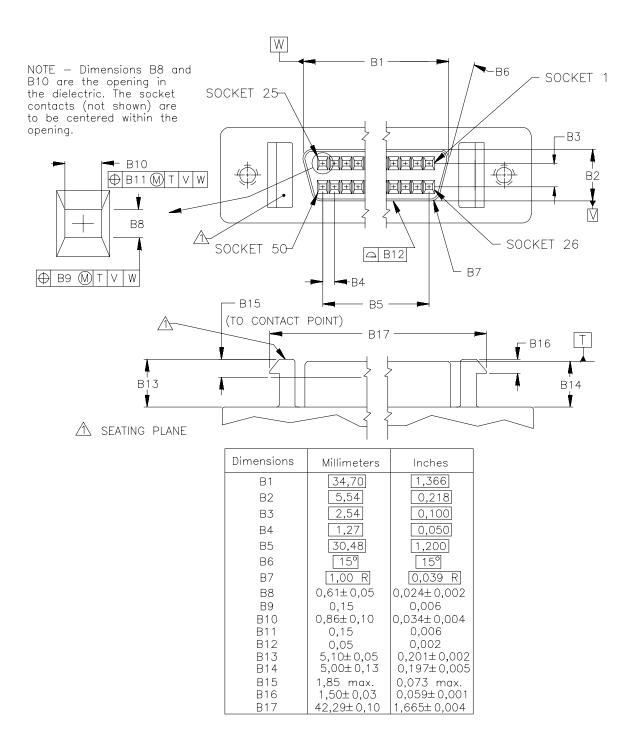

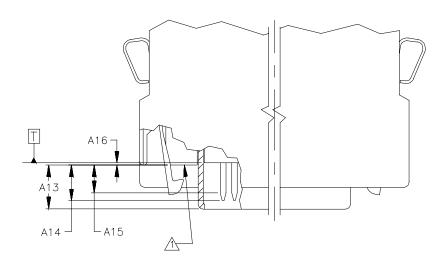

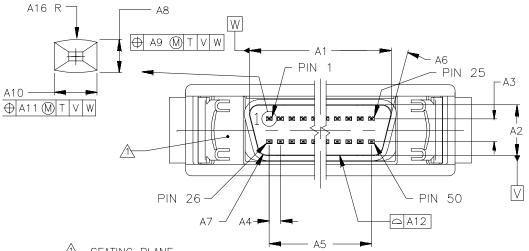

| 12 80-contact alternative 4 nonshielded SCSI device connector (P cable)                                                                                 |      |

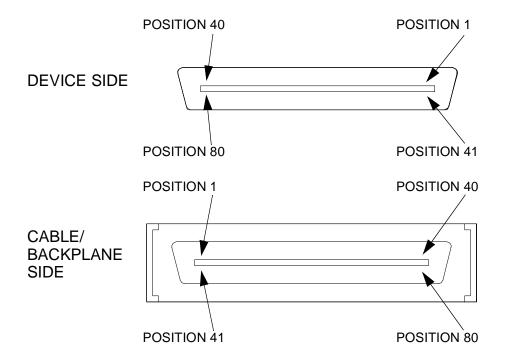

| 13 80-contact alternative 4 nonshielded contact positions                                                                                               |      |

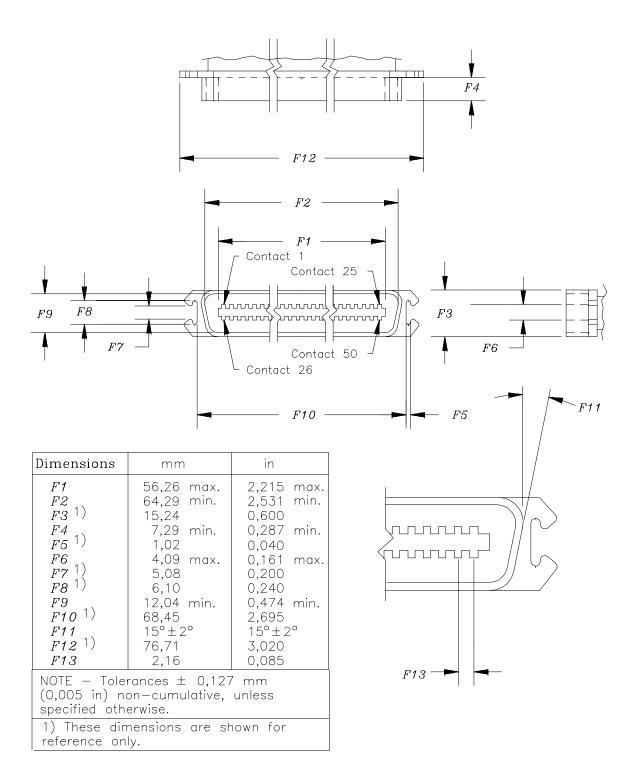

| 14 50-contact alternative 1 shielded SCSI device connector (A cable)                                                                                    |      |

| 15 50-contact alternative 1 shielded mating connector (A cable)                                                                                         |      |

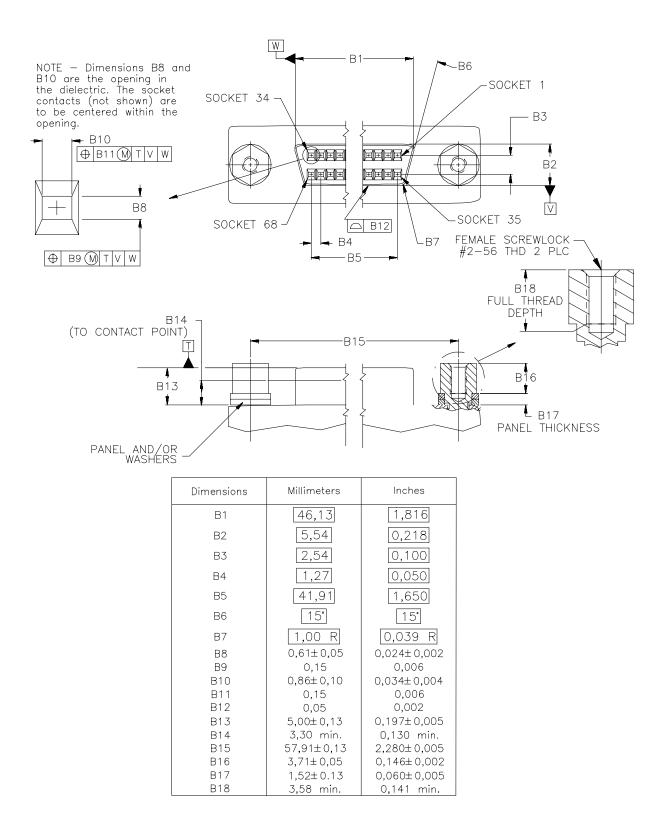

| 16 50-contact alternative 2 shielded SCSI device connector (A cable)                                                                                    |      |

| 17 50-contact alternative 2 shielded mating connector (A cable)                                                                                         |      |

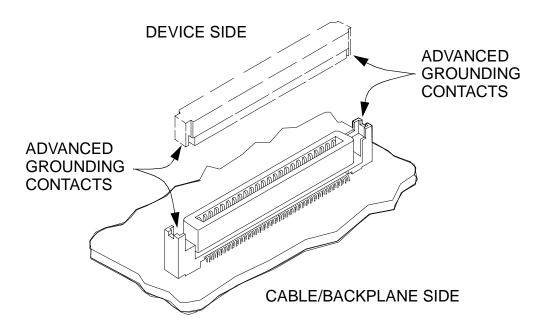

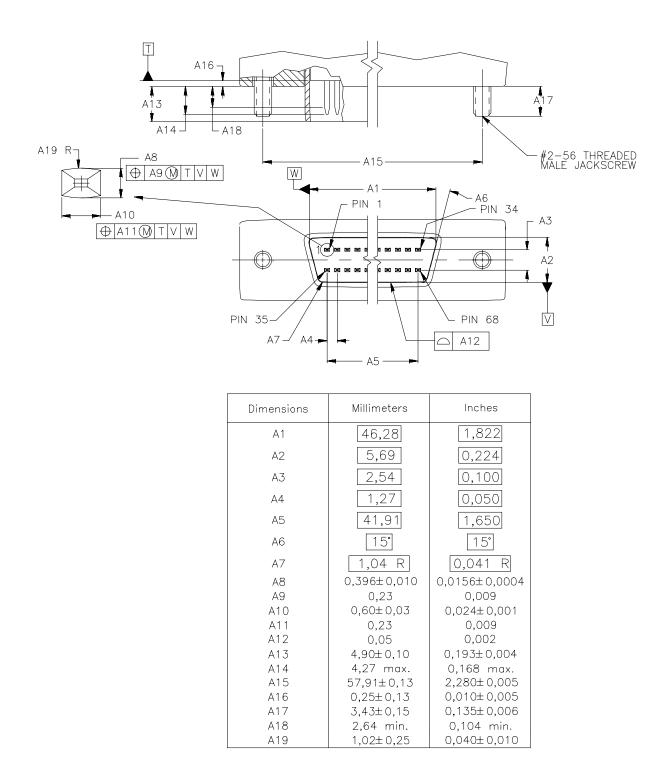

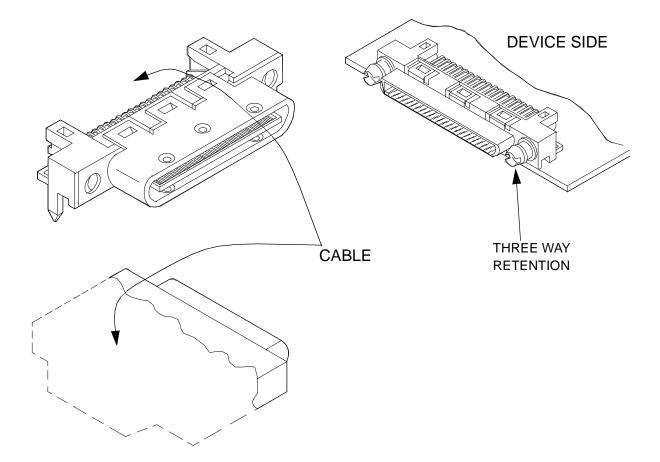

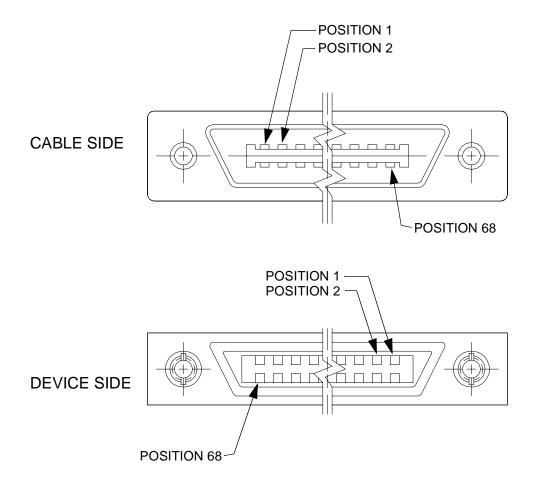

| 18 68-contact alternative 3 shielded SCSI device connector (P cable/Q cable)                                                                            |      |

| 19 68-contact alternative 3 shielded mating connector (P cable/Q cable)<br>20 68-contact alternative 4 shielded SCSI device connector (P cable/Q cable) |      |

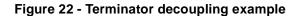

| 21 68-contact alternative 4 shielded contact positions (P cable/Q cable)                                                                                |      |

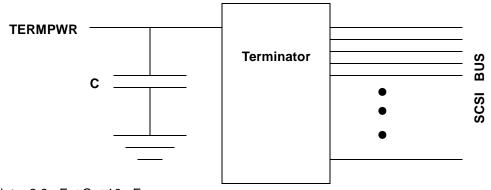

| 22 Terminator decoupling example                                                                                                                        |      |

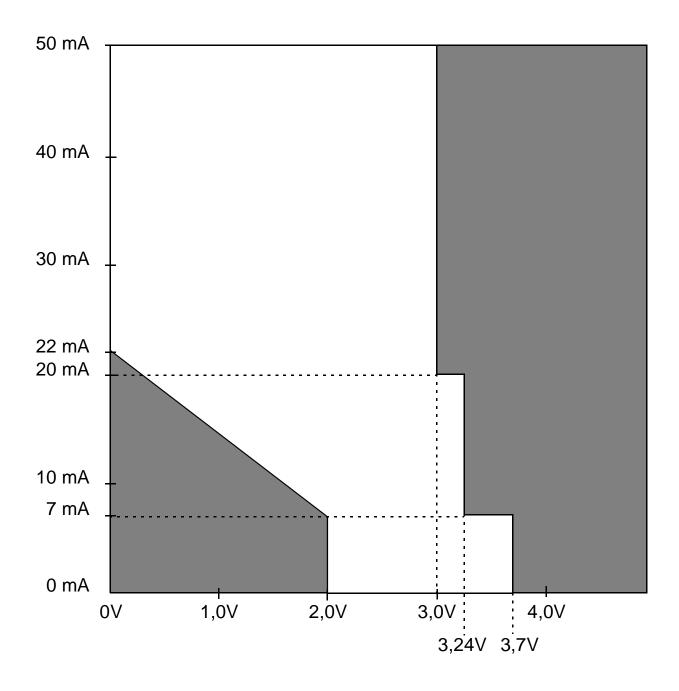

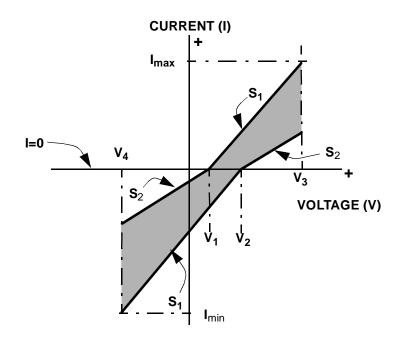

| 23 Active negation current vs. voltage                                                                                                                  |      |

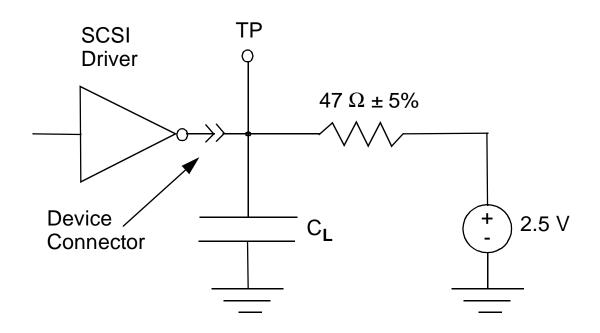

| 24 SE A.C. test circuit                                                                                                                                 |      |

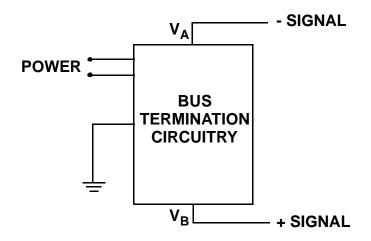

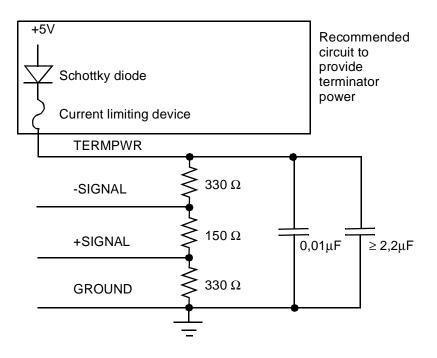

| 25 Differential SPI-2 bus terminator                                                                                                                    |      |

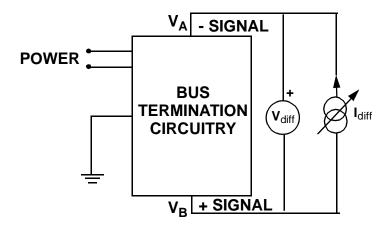

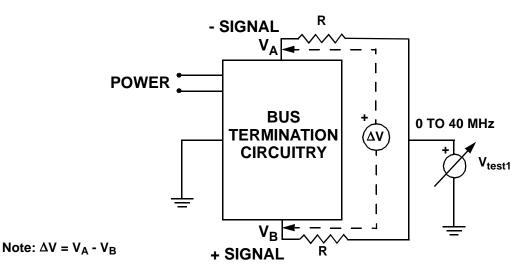

| 26 Test circuit for terminator differential impedance                                                                                                   |      |

| 27 Termination I-V characteristics for differential and common mode impedance tests                                                                     |      |

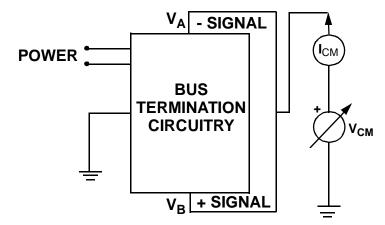

| 28 Test circuit for termination common mode impedance test                                                                                              |      |

| 29 Termination balance test configuration                                                                                                               |      |

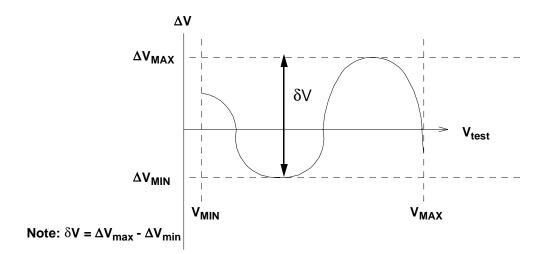

| 30 Termination balance test data definition                                                                                                             |      |

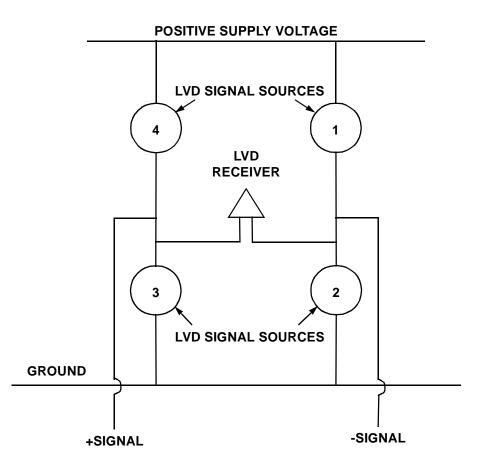

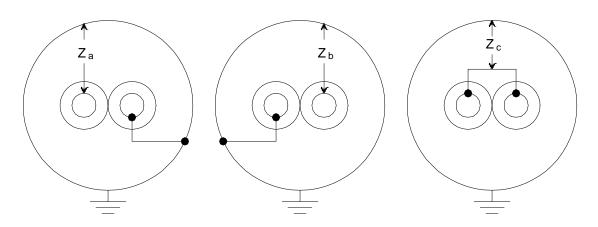

| 31 LVD transceiver architecture                                                                                                                         |      |

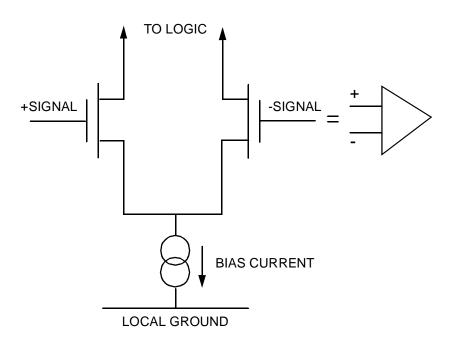

| 32 LVD receiver example                                                                                                                                 |      |

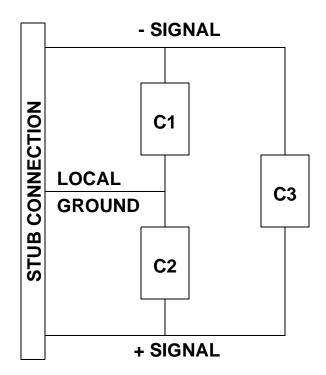

| 33 Capacitive loads                                                                                                                                     |      |

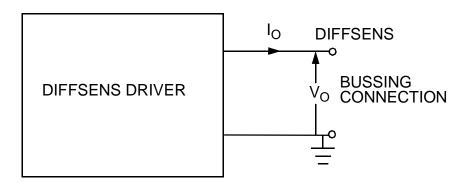

| 34 LVD DIFFSENS driver signal definitions                                                                                                               |      |

| 35 DIFFSENS receiver function                                                                                                                           |      |

| 36 LVD DIFFSENS receiver example                                                                                                                        |      |

| 37 Multimode terminator architecture                                                                                                                    |      |

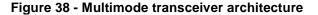

| 38 Multimode transceiver architecture                                                                                                                   | 74   |

| 39 HVD test circuit                                                                                                                                     | 78   |

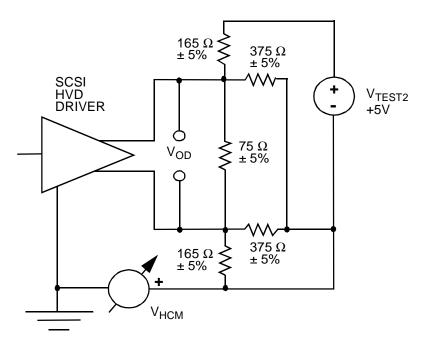

| 40 SE driver protection circuit                                                                                                                         | 80   |

| 41 Voltage and current definitions                                                                                                                      |      |

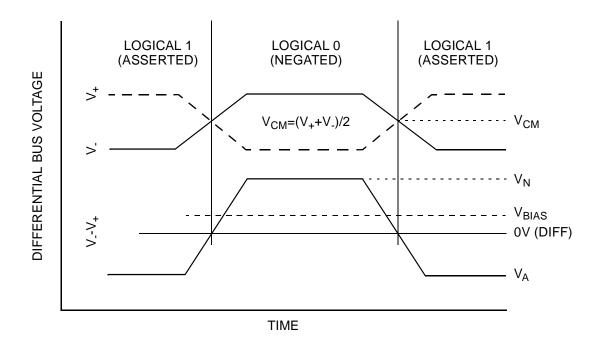

| 42 Signaling sense                                                                                                                                      |      |

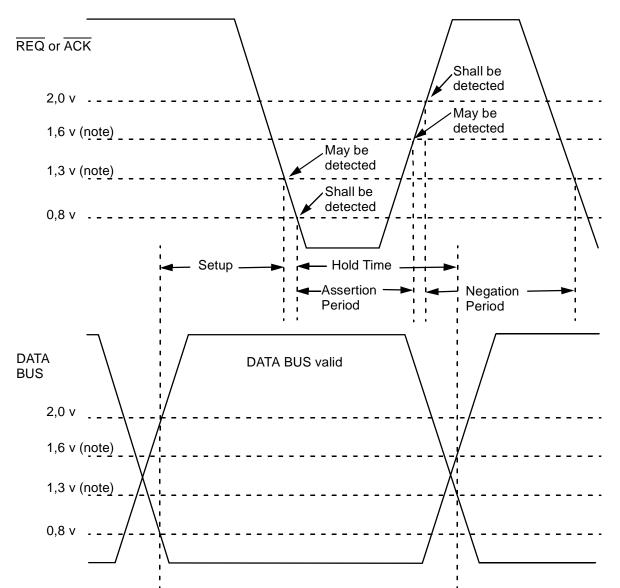

| 43 Fast-10 SE timing measurement points                                                                                                                 |      |

| 44 Fast-20 SE timing measurement points                                                                                                                 | 94   |

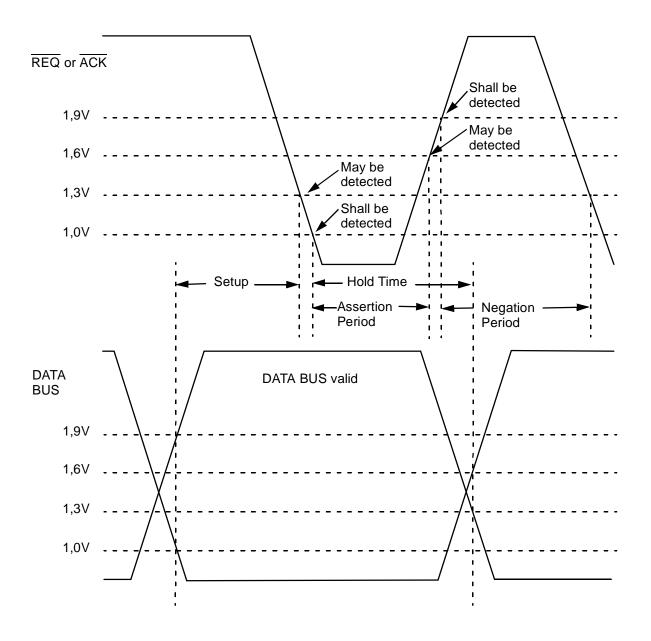

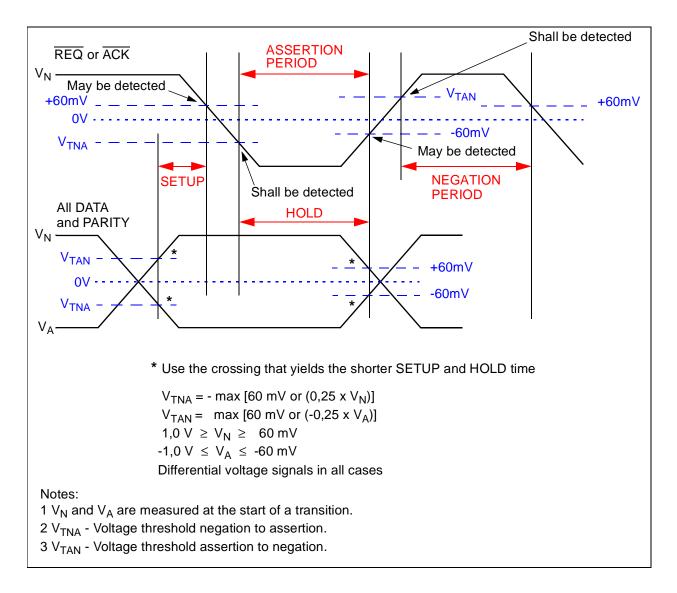

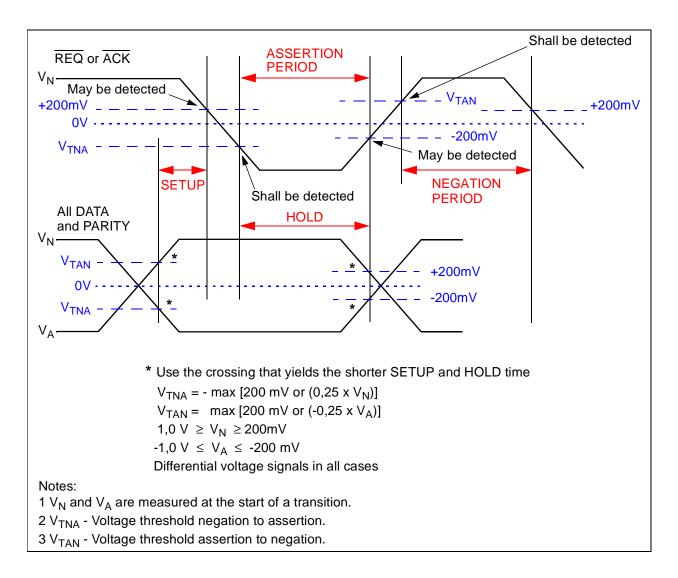

| 45 LVD timing measurement points                                                                                                                        | 95   |

| 46 HVD timing measurement points                                                                                                                        |      |

| 47 Fast-10 setup and hold times for SE applications                                                                                                     |      |

| 48 Fast-10 setup and hold timing for HVD applications                                                                                                   |      |

| 49 Fast-20 setup and hold times for SE applications                                                                                                     |      |

| 50 Fast-20 setup and hold timing for HVD applications                                                                                                   |      |

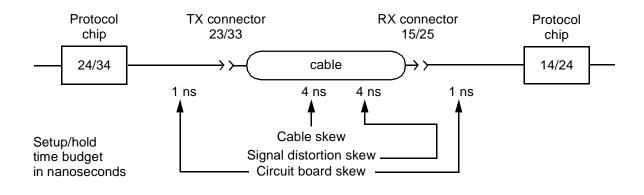

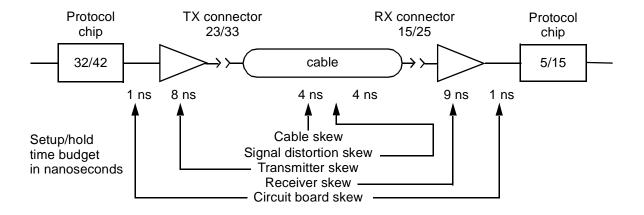

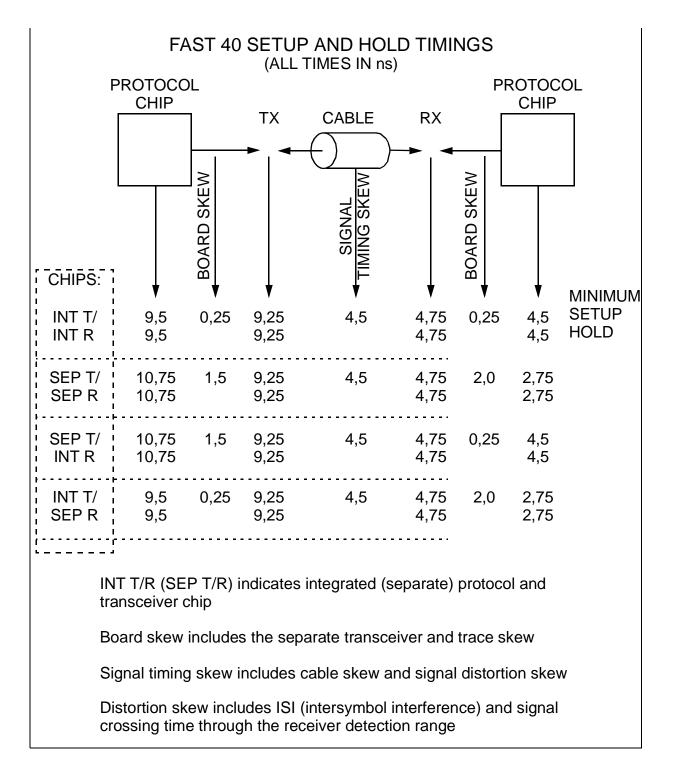

| 51 Fast-40 System setup and hold timings (all times in ns)                                                                                              |      |

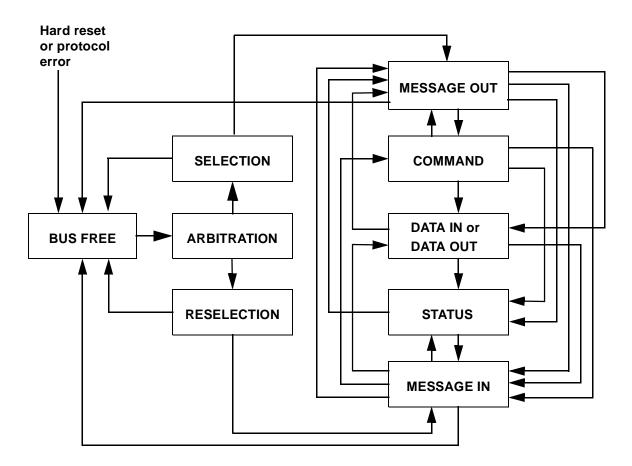

| 52 Phase sequences                                                                                                                                      |      |

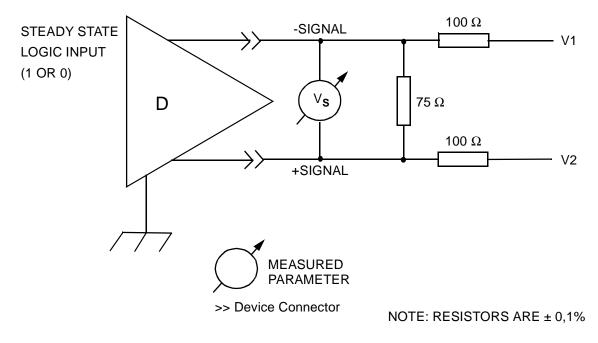

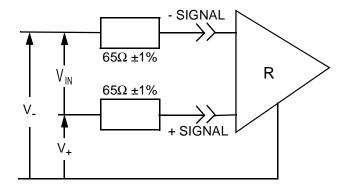

| A.1 Differential steady-state output voltage test circuit                                                                                               |      |

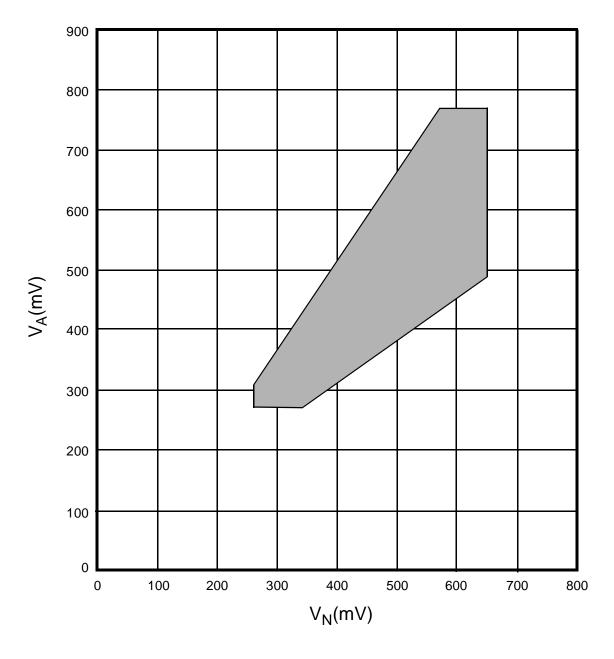

| A.2 Domain for driver assertion and negation levels                                                                                                     |      |

| A.3 Driver offset steady-state voltage test circuit                                                                                                     | 148  |

|                                                                                                                                                         |      |

| A.4 Common mode output voltage test                          |  |

|--------------------------------------------------------------|--|

| A.5 Driver short-circuit test circuit                        |  |

| A.6 Open-circuit output voltage test circuit                 |  |

| A.7 Differential output switching voltage test circuit       |  |

| A.8 Driver output signal waveform                            |  |

| A.9 Driver offset switching voltage test circuit             |  |

| A.10 Receiver input voltage threshold test circuit           |  |

| A.11 Transceiver off-state output current test circuit       |  |

| B.1 Transfer cycles                                          |  |

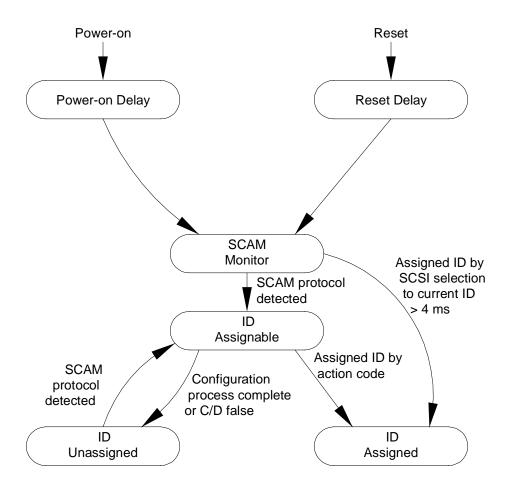

| B.2 Level 1 SCAM target states                               |  |

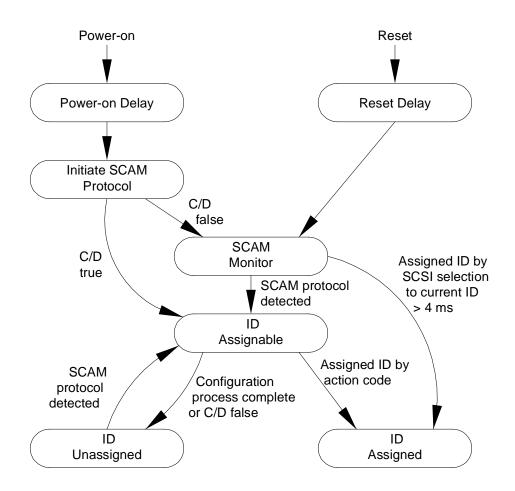

| B.3 Level 2 SCAM target states                               |  |

| D.1 Sample circuit for mated indications                     |  |

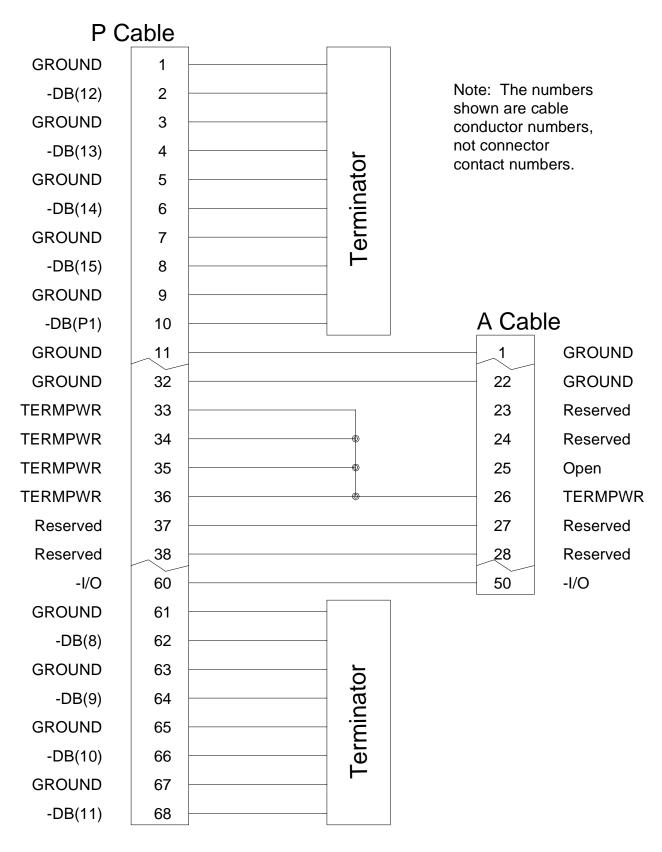

| E.1 Interconnecting single-ended A and P cables              |  |

| E.2 Interconnecting HVD A and P cables                       |  |

| F.1 Differential impedance measurement                       |  |

| G.1 Minimum device spacing versus bus and device capacitance |  |

| I.1 SE icon for SCSI                                         |  |

| I.2 LVD icon for SCSI                                        |  |

| I.3 SE/LVD multimode icon for SCSI                           |  |

| I.4 HVD icon for SCSI                                        |  |

| J.1 Example of termination network for HVD devices           |  |

Technical Committee T10 on Lower Level Interfaces, which approved this standard, had the following members:

John B. Lohmeyer, Chair Lawrence J. Lamers, Vice-Chair Ralph O. Weber, Secretary

T10 membership list to be inserted during final ANSI edit.

## Foreword

This foreword is not part of ANSI NCITS. - 199x.

The SCSI Parallel Interface-2 standard is divided into the following clauses:

- Clause 1 is the scope;

- Clause 2 enumerates the normative references that apply to this standard;

- Clause 3 describes the definitions, symbols, conventions and abbreviations used in this standard;

- Clause 4 describes the SCSI parallel interface model used in this standard;

- Clause 5 describes the connectors;

- Clause 6 describes the cable characteristics;

- Clause 7 describes the electrical characteristics;

- Clause 8 describes the SCSI bus signals;

- Clause 9 describes the bus timing;

- Clause 10 describes the removal and insertion of parallel SCSI devices;

- Clause 11 describes the SCSI parallel protocol characteristics;

Annexes A, B, C and D form an integral part of this standard. Annexes E to K are for information purposes only.

Requests for interpretation, suggestions for improvement and addenda, or defect reports are welcome. They should be sent to the NCITS Secretariat, ITI, 1250 Eye Street, NW, Suite 200, Washington, DC 20005-3922.

This working draft will be processed and approved for submittal to ANSI by National Committee For Information Technology Standards, NCITS. Committee approval of this standard does not necessarily imply that all committee members voted for approval.

At the time it approved this standard, NCITS had the following members:

## Introduction

The SCSI protocol is designed to provide an efficient peer-to-peer I/O bus with the maximum number of hosts and peripherals determined by the bus width (typically 8 or 16 with 32 allowed). Data may be transferred asynchronously or synchronously at rates that depend primarily on device implementation and cable length.

SCSI is an I/O interface that may be operated over a wide range of media and transfer rates. The objectives of the parallel interface in SCSI are:

a) To provide host computers with device independence within a class of devices. Thus, different disk drives, tape drives, printers, optical media drives, and other devices may be added to the host computers without requiring modifications to generic system hardware. Vendor unique indications are accommodated. Reserved areas are provided for future standardization.

b) To provide interoperability with SCSI-2 devices. Devices meeting SCSI-2 and the SCSI Parallel Interface-2 standards co-exist on the same bus. SCSI-3 devices should be permissive of the SCSI-2 or SCSI-3 compliant behavior of other devices including those not implementing optional extensions of the SCSI Parallel Interface-2 Standard.

The interface protocol includes provision for the connection of multiple initiators (SCSI devices capable of initiating a task) and multiple targets (SCSI devices capable of responding to a request to perform a task). Distributed arbitration (i.e., bus-contention logic) is built into the architecture of parallel SCSI. A default priority system awards interface control to the highest priority SCSI device that is contending for use of the bus and an optional fairness algorithm is defined.

With any technical document there may arise questions of interpretation as new products are implemented, The NCITS Committee has established procedures to issue technical opinions concerning the standards developed by the NCITS organization. These procedures may result in SCSI Technical Information Bulletins being published by NCITS.

Any such bulletins, while reflecting the opinion of the Technical Committee that developed the standard, are intended solely as supplementary information to other users of the standard. This standard, ANSI NCITS. - 199x, as approved though the publication and voting procedures accredited by the American National Standards Institute, is not altered by these bulletins. Any subsequent revision to this standard may or may not reflect the contents of any such Technical Information Bulletins.

Current NCITS practice is to make Technical Information Bulletins available through:

| Global Engineering       | Telephone: | 303-792-2181 or |

|--------------------------|------------|-----------------|

| 15 Inverness Way East    |            | 800-854-7179    |

| Englewood, CO 80112-5704 | Facsimile: | 303-792-2192    |

T10/1142D revision 20b

## 1 Scope

This standard defines the mechanical, electrical, timing, and protocol requirements of the SCSI parallel interface to allow conforming devices to inter-operate. The SCSI parallel interface is a local I/O bus that may be operated over a wide range of transfer rates. The objectives of the SCSI parallel interface are

a) To provide host computers with device independence within a class of devices. Thus, different disk drives, tape drives, printers, optical media drives, and other devices may be added to the host computers without requiring modifications to generic system hardware. Provision is made for the addition of special features and functions through the use of vendor-specific options. Reserved areas are provided for future standardization.

b) To provide compatibility such that properly conforming SCSI-2 devices may interoperate with SCSI-3 devices given that the systems engineering is correctly done. Properly conforming SCSI-2 devices should respond in an acceptable manner to reject SCSI-3 protocol extensions. SCSI-3 protocol extensions are designed to be permissive of such rejections and thus allow the SCSI-2 devices to continue operation without requiring the use of the extension.

The interface protocol includes provision for the connection of multiple initiators (SCSI devices capable of initiating an I/O process) and multiple targets (SCSI devices capable of responding to a request to perform an I/O process). Distributed arbitration (i.e., bus-contention logic) is built into the architecture of SCSI. A default priority system awards interface control to the highest priority SCSI device that is contending for use of the bus and an optional fairness algorithm is defined.

This standard defines the physical attributes of an input/output bus for interconnecting computers and peripheral devices.

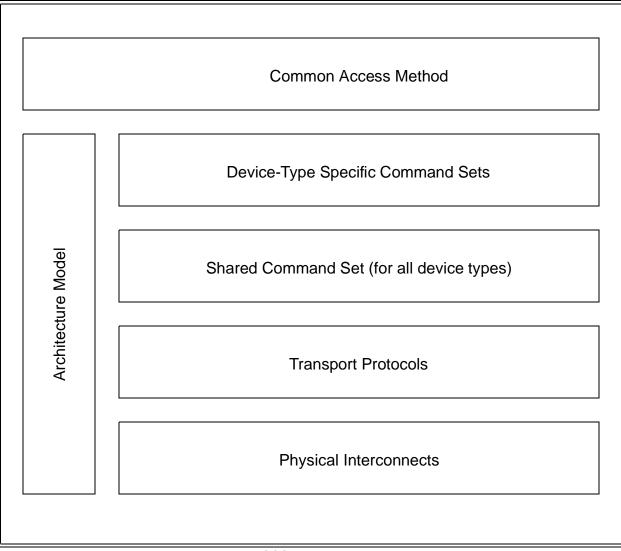

Figure 1 is intended to show the general structure of SCSI standards. The figure is not intended to imply a relationship such as a hierarchy, protocol stack, or system architecture.

Figure 1 - SCSI document road map

At the time this standard was generated examples of the SCSI general structure included:

**Physical Interconnects:**

Fibre Channel Arbitrated Loop [X3.272-1996] Fiber Channel - Physical and Signaling Interface [X3.230-1994] High Performance Serial Bus [IEEE 1394-1995] SCSI Parallel Interface - 2 [this standard] Serial Storage Architecture Physical Layer 1 [X3.293-1996] Serial Storage Architecture Physical Layer 2 [NCITS.307-199x]

Transport Protocols:

Serial Storage Architecture Transport Layer 1 [X3.295-1996] SCSI-3 Fiber Channel Protocol [X3.269-1996] SCSI Fiber Channel Protocol - 2 [T10/1144D] SCSI Serial Bus Protocol - 2 [T10/1155D] Serial Storage Architecture SCSI-2 Protocol [X3.294-1996] Serial Storage Architecture SCSI-3 Protocol [NCITS.309-199x] Serial Storage Architecture Transport Layer 2 [NCITS.308-199x]

Shared Command Set:

SCSI-3 Primary Commands Standard [X3.301-1997] SCSI Primary Commands-2 Standard [T10/1236D]

Device-Type Specific Commands Sets:

SCSI-3 Block Commands [NCITS.306-199x] SCSI-3 Enclosure Services [NCITS.305-199x] SCSI-3 Stream Commands [T10/997D] SCSI-3 Medium Changer Commands [T10/999D] SCSI-3 Controller Commands [X3.276-1997] SCSI Controller Commands - 2 [T10/1225D] SCSI-3 Multimedia Command Set [X3.304-199x] SCSI Multimedia Command Set - 2 [T10/1228D]

Architecture Model:

SCSI-3 Architecture Model [X3.270-1996] SCSI Architecture Model - 2 [T10/1157D]

Common Access Method:

SCSI Common Access Method [X3.232-1996] SCSI Common Access Method - 3 [T10/990D]

The term SCSI is used wherever it is not necessary to distinguish between the versions of SCSI. The Small Computer System Interface - 2 (ANSI X3.131-1994) is referred to herein as SCSI-2. The term SCSI-3 in this standard refers to versions of SCSI defined since SCSI-2.

#### 2 Normative references

The following standards contain provisions which, through reference in the text, constitute provisions of this standard. At the time of publication, the editions indicated were valid. All standards are subject to revision, and parties to agreements based on this standard are encouraged to investigate the possibility of applying the most recent editions of the standards listed below.

Copies of the following documents may be obtained from ANSI: approved ANSI standards, approved and draft international and regional standards (ISO, IEC, CEN/CENELEC, ITUT), and approved and draft foreign standards (including BSI, JIS, and DIN). For further information, contact ANSI Customer Service Department at 212-642-4900 (phone), 212-302-1286 (fax) or via the World Wide Web at http://www.ansi.org.

Additional availability contact information is provided below as needed.

#### 2.1 Approved references

Small Computer System Interface - 2, ANSI X3.131-1994

SCSI-3 Architecture Model standard, ANSI X3.270 - 1996

SCSI-3 Primary Commands Standard, ANSI X3.301 - 1997

Information technology - Telecommunications and information exchange between systems - Twisted pair multipoint interconnections, ISO/IEC 8482:1993-12

Detail Specification for Trapezoidal Connectors with Non-removable Ribbon Contacts on 1.27 mm

Pitch Double Row used with Single Connector Attachments (SCA-2), EIA-700A0AE (SP-3651)

Detail Specification for Trapezoidal Connector 0.8mm Pitch used with Very High Density Cable Interconnect (VHDCI),EIA-700A0AF (SP-3652) Low Level Contact Resistance Test Procedure for Electric Connectors, EIA 364-23A

## 2.2 References under development

At the time of publication, the following referenced standards were still under development. For information on the current status of the document, or regarding availability, contact the relevant standards body or other organization as indicated.

SCSI Architecture Model-2 standard, T10/1157D

NOTE 1 - For more information on the current status of the document, contact the NTCIS Secretariat at 202-737-8888 (phone), 202-638-4922 (fax) or via Email at nctis@itic.nw.dc.us. To obtain copies of this document, contact Global Engineering at 15 Inverness Way, East Englewood, CO 80112-5704 at 303-792-2181 (phone), 800-854-7179 (phone), or 303-792-2192 (fax).

#### 2.3 Other references

For information on the current status of the listed document(s), or regarding availability, contact the indicated organization.

SCA-2 Unshielded Connections, SFF-8451 VHDCI Shielded Configurations, SFF-8441

NOTE 2 - For more information on the current status of the document, contact the SFF committee at 408-867-6630 (phone), or 408-867-2115 (fax). To obtain copies of this document, contact the SFF committee at 14426 Black Walnut Court, Saratoga, CA 95070 at 408-867-6630 (phone) or 408-741-1600 (fax).

Standard Test Methods for Electrical Performance Properties of Insulations and Jackets for Telecommunications Wire and Cable, ASTM D-4566

#### 3 Definitions, symbols, abbreviations, and conventions

#### 3.1 Definitions

**3.1.1 A cable:** A 50-conductor cable (see 3.1.45 and 3.1.51) that provides a primary 8-bit DATA BUS and control signals.

**3.1.2 ACKx:** A bus signal that is either the ACK or ACKQ signal.

**3.1.3 agent:** Carries out the actions of a requested service following the rules of the protocol.

**3.1.4 application client:** An object that is the source of SCSI commands. Further definition of an application client is found in the SCSI-3 Architecture Model standard.

**3.1.5 asynchronous event notification:** A procedure used by targets to notify initiators of events that occur when a pending task does not exist for that initiator.

**3.1.6 asynchronous transfer:** An information transfer that uses the asynchronous REQ/ACK handshake.

**3.1.7 auto-contingent allegiance:** A condition of a task set following the return of a CHECK CONDITION or COMMAND TERMINATED status. See the SCSI-3 Architecture Model standard for a detailed definition of auto-contingent allegiance.

**3.1.8 bus path:** The electrical path directly between the bus terminators.

**3.1.9 byte:** Indicates an 8-bit construct.

**3.1.10 confirmation:** The last step of a confirmed service informing the upper protocol layer that the requested service has been completed.

**3.1.11 confirmed protocol service:** A service available at the protocol service interface, that requires confirmation of completion.

**3.1.12 contact:** The electrically-conductive portion of a connector associated with a single conductor in a cable.

**3.1.13 contingent allegiance:** One of the conditions of a task set following the return of a CHECK CONDITION or COMMAND TERMINATED status. A detailed definition of contingent allegiance may be found in SCSI-2.

**3.1.14 current task:** A task that is in the process of sending messages, status, transferring data, or transferring command data to or from the initiator.

3.1.15 data bus: An 8-bit,16-bit or 32-bit data bus (see 8.1).

**3.1.16 device server:** An object within the logical unit which executes SCSI tasks according to the rules for task management as described in the SCSI-3 Architecture Model standard.

**3.1.17 differential:** A signalling alternative that employs differential drivers and receivers to improve signal-to-noise ratios and increase maximum cable lengths (also see 3.1.69 SE). Includes both LVD (see 7.2) and HVD (see 7.4) differential drivers and receivers.

**3.1.18 disconnect:** The action that occurs when a SCSI device releases control of the SCSI bus, allowing it to go to the BUS FREE phase.

**3.1.19 driver:** The circuitry used to control the state of the bus.

**3.1.20 exception condition:** Any event that causes a SCSI device to enter an auto-contingent allegiance or contingent allegiance condition.

**3.1.21 fast-5:** Negotiated to receive synchronous data at a transfer rate less than or equal to 5 megatransfers per second. Note: Previous SCSI standards referred to this transfer range as slow.

**3.1.22 fast-10:** Negotiated to receive synchronous data at a transfer rate greater than 5 megatransfers per second and less than or equal to a transfer rate of 10 megatransfers per second. Note: Previous SCSI standards referred to this transfer range as fast SCSI.

**3.1.23 fast-20:** Negotiated to receive synchronous data at a transfer rate greater than 10 megatransfers per second and less than or equal to a transfer rate of 20 megatransfers per second.

**3.1.24 fast-40:** Negotiated to receive synchronous data at a transfer rate greater than 20 megatransfers per second and less than or equal to a transfer rate of 40 megatransfers per second.

3.1.25 flag: An abstraction indicating that the condition will be communicated to the recipient of the flag.

**3.1.26 field:** A group of one or more contiguous bits.

**3.1.27 indication:** The second step of a four step confirmed service in reply to a request.

**3.1.28 initial connection:** An initial connection is the result of a connect. It exists from the assertion of the BSY signal (see 11.1.2) in a SELECTION phase until the next BUS FREE phase.

**3.1.29 initiator:** An SCSI device containing application clients that originate device service and task management requests to be processed by a target SCSI device. See the SCSI-3 Architecture Model standard for a detailed definition of an initiator.

**3.1.30 I\_T nexus:** A nexus which exists between an initiator and a target.

**3.1.31 I\_T\_L nexus:** A nexus which exists between an initiator, a target, and a logical unit. This relationship replaces the prior I\_T nexus.

**3.1.32** I\_T\_L\_Q nexus: A nexus between an initiator, a target, a logical unit, and a queue tag following the successful receipt of one of the queue tag messages. This relationship replaces the prior I\_T\_L nexus.

**3.1.33 logical unit:** An externally addressable entity within a target that implements an SCSI device model. See the SCSI-3 Architecture Model standard for a detailed definition of a logical unit.

3.1.34 logical unit number: An identifier for a logical unit.

**3.1.35 I/O process:** An I/O process consists of one initial connection and zero or more reconnections, all pertaining to a single task or a group tasks. An I/O process begins with the establishment of a nexus. An I/O process normally ends with the BUS FREE phase (see 11.1.1).

3.1.36 magnitude: The absolute value of a number or quantity.

**3.1.37 mandatory:** The referenced item is required to claim compliance with this standard.

**3.1.38 megatransfers per second:** The repetitive rate at which data are transferred across the bus. This is equivalent to megabytes per second on an 8-bit wide bus.

**3.1.39 message:** One or more bytes transferred between an initiator and a target to do link control, task management, and to attach task attributes to commands.

**3.1.40 multimode single-ended (MSE):** A signalling alternative for multimode SCSI devices that employs MSE (see 7.3) drivers and receivers to allow multimode SCSI devices to operate when SE SCSI devices are present on the bus.

**3.1.41 nexus:** A relationship between an initiator and a target that begins with an initial connection and ends with the completion of the associated I/O process. This relationship is formed as the result of a task.

**3.1.42 object:** An architectural abstraction that encapsulates data types, services, or other objects that are related in some way.

**3.1.43 odd parity:** Odd logical parity, where the parity bit is driven and verified to be that value that makes the number of assertions on the associated data byte plus the parity bit equal to an odd number (1, 3, 5, 7, or 9). See 3.1.19, parity bit.

**3.1.44 one:** A true signal value or a true condition of a variable.

**3.1.45 P cable:** A 68-conductor cable that provides the primary 16-bit DATA BUS and control signals.

**3.1.46 parity bit:** A bit associated with a byte that is used to detect the presence of single-bit errors within the byte. The parity bit is driven such that the number of logical ones in the byte plus the parity bit is odd.

**3.1.47 path:** The cable, printed circuit board or other means for providing the conductors and insulators that connect two or more points.

**3.1.48 pending task:** A task that is not the current task.

**3.1.49 port:** A single attachment to an SCSI bus from an SCSI device.

**3.1.50 primary bus:** The bus that contains the first 8 or 16 bits of the data and the control signals used to operate SCSI devices.

**3.1.51 Q cable:** A 68-conductor cable that provides the secondary 16-bit DATA BUS. This cable is used in conjunction with the P cable to provide a 32-bit data path.

**3.1.52 queue:** The arrangement of tasks within a task set usually according to the temporal order in which they were created.

**3.1.53 queue tag:** The parameter associated with a task that uniquely identifies it from other tagged tasks for a logical unit from the same initiator.

**3.1.54 receiver:** The circuitry used to detect the state of the bus.

**3.1.55 reconnect:** The act of resuming a nexus to continue a task. A target reconnects when conditions are appropriate for the physical bus to transfer data associated with a nexus between an initiator and a target.

**3.1.56 reconnection:** A reconnection is the result of a reconnect and it exists from the receipt of a selection confirmation with the selection won flag set to one or a reselection confirmation with the reselection won flag set to one until the next bus free indication occurs.

**3.1.57 request:** A transaction invoking a service.

**3.1.58 REQx:** A bus signal that is either the REQ or REQQ signal.

**3.1.59 reselection ID:** The bit-significant representation of the target SCSI address in combination with the initiator SCSI address that is the result of a successful reselection service request.

**3.1.60 response:** The third step of a four set confirmed service in reply to an indication.

**3.1.61 SCSI address:** The decimal representation of the unique address assigned to an SCSI device.

**3.1.62 SCSI bus:** The consists of all the conductors and connectors required to attain signal line continuity between every driver, receiver, and terminator for each signal.

**3.1.63 SCSI device:** A device containing at least one SCSI port and the means to connect the drivers and receivers to the bus.

**3.1.64 SCSI ID:** The bit-significant representation of the SCSI address.

**3.1.65 secondary bus:** The bus that contains 16 bits of the data and is used in conjunction with a primary bus to create a 32-bit data path.

**3.1.66 signal assertion:** The act of driving a signal to the true state.

**3.1.67 signal negation:** The act of performing a signal release or of driving a signal to the false state.

**3.1.68 signal release:** The act of allowing the cable terminators to bias the signal to the false state (by placing the driver in the high impedance condition).

**3.1.69 single-ended (SE):** A signalling alternative that employs SE (see 7.1) drivers and receivers to increase circuit density (also see 3.1.17, differential).

**3.1.70 source (a signal):** The act of either signal assertion, signal negation, or signal release.

**3.1.71 stub:** Any electrical path connected to the bus that is not part of the bus path.

**3.1.72 stubbed path:** Path with stubs attached.

**3.1.73 target**: An SCSI device that receives SCSI commands and directs such commands to one or more logical units.

**3.1.74 task:** An object within the logical unit representing the work associated with a command or group of linked commands. A task consists of one initial connection and zero or more reconnections, all pertaining to the task. A task causes the nexus to be generated.

3.1.75 task manager: A server within the target device which executes task management functions.

**3.1.76 task management function:** A task manager service which can be invoked by an application client to affect the execution of one or more tasks.

**3.1.77 task set:** A group of tasks within a target device, whose interaction is dependent on the task management, contingent allegiance and auto-contingent allegiance rules. See the SCSI-3 Architecture Model standard for a detailed definition of a task set.

3.1.78 transceiver: A device that implements both the SCSI bus receiver and driver functions.

**3.1.79 upper level protocol:** Any protocol executed through services provided by a lower level protocol.

**3.1.80 unconfirmed protocol service:** A service available at the protocol service interface, that does not result in a completion confirmation.

**3.1.81 vendor-specific:** Something (i.g., a bit, field, code value) that is not defined by this standard and may be used differently in various implementations.

**3.1.82 zero:** A false signal value or a false condition of a variable.

#### 3.2 Symbols and abbreviations

| ≠ or NE | not equal                               |

|---------|-----------------------------------------|

| ≤ or LE | less than or equal to                   |

| ±       | plus or minus                           |

| ~       | approximately                           |

| х       | multiply                                |

| +       | add                                     |

| -       | subtract                                |

| < or LT | less than                               |

| = or EQ | equal                                   |

| > or GT | greater than                            |

| ≥ or GE | greater than or equal to                |

| ACA     | auto-contingent allegiance (see 3.1.7)  |

| AWG     | American wire gauge                     |

| CA      | Contingent allegiance (see 3.1.13)      |

| CMOS    | Complementary metal oxide semiconductor |

| EMI     | Electro-magnetic interference           |

| EMC     | Electro-magnetic compatibility          |

| ESD     | Electro-static discharge                |

| HVD     | High voltage differential               |

| IDC     | Insulation displacement contact         |

| LSB    | Least significant bit                    |

|--------|------------------------------------------|

| LUN    | Logical unit number                      |

| LVD    | Low voltage differential                 |

| MLVD   | Multimode low voltage differential       |

| MSB    | Most significant bit                     |

| MSE    | Multimode single ended                   |

| RFI    | Radio frequency interface                |

| RIRC   | Request indication response confirmation |

| SCSI   | Either SCSI-2 or SCSI-3.                 |

| SCSI-2 | Small Computer System Interface - 2      |

| SCSI-3 | Small Computer System Interface - 3      |

| SDTR   | Synchronous data transfer request        |

| SE     | Single-ended                             |

| WDTR   | Wide data transfer request               |

## 3.3 Keywords

**3.3.1 expected:** A keyword used to describe the behavior of the hardware or software in the design models assumed by this standard. Other hardware and software design models may also be implemented.

**3.3.2 invalid:** A keyword used to describe an illegal or unsupported bit, byte, word, field or code value. Receipt of an invalid bit, byte, word, field or code value shall be reported as error.

**3.3.3 mandatory:** A keyword indicating an item that is required to be implemented as defined in this standard to claim compliance with this standard.

**3.3.4 may:** A keyword that indicates flexibility of choice with no implied preference.

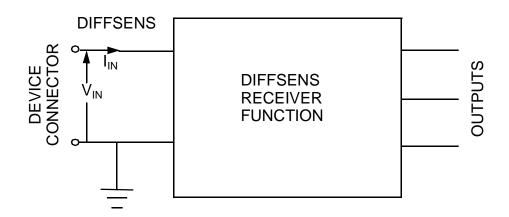

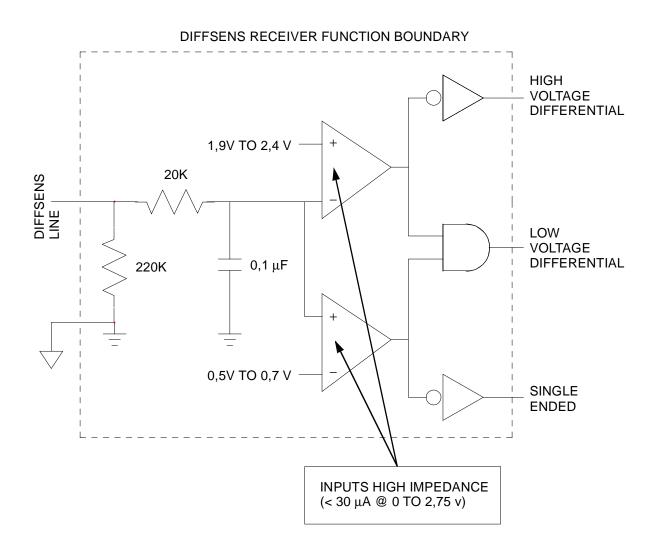

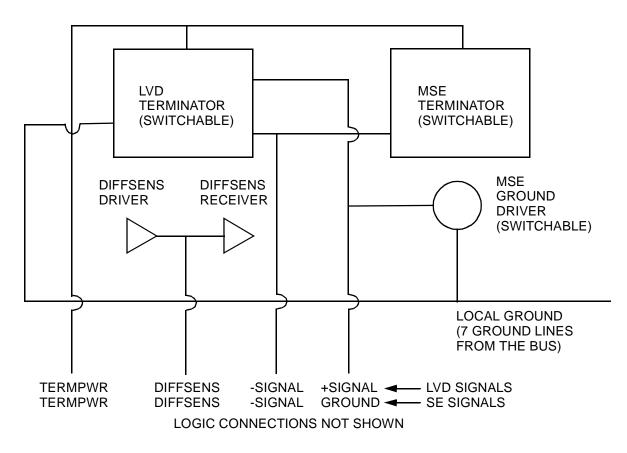

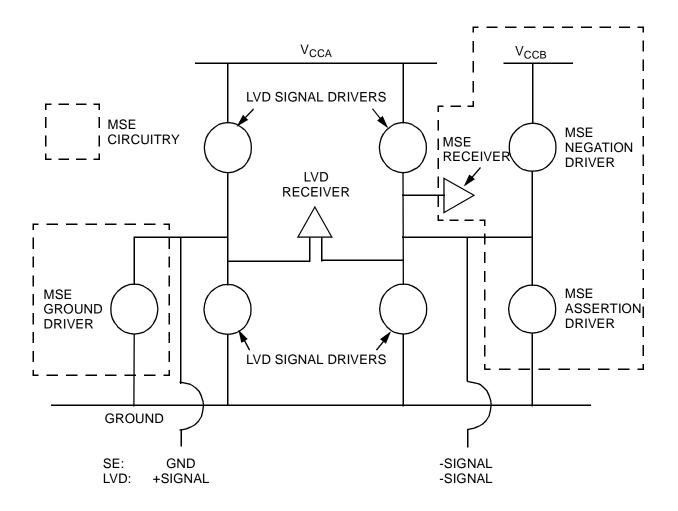

**3.3.5 optional:** A keyword that describes features that are not required to be implemented by this standard. However, if any optional feature defined by this standards is implemented, it shall be implemented as defined in this standard.