# Symbios Logic PCI-SCSI I/O Processors

Programming Guide Version 2.1

J25972I

The products described in this publication are products of Symbios Logic Inc.

SCRIPTS and NASM are trademarks and TolerANT is a registered trademark of Symbios Logic Inc.

Ultra SCSI is the term used by the SCSI Trade Association to describe Fast-20 SCSI, as documented in the SCSI-3 Fast-20 Parallel Interface standard, X3.277-199X. Ultra2 SCSI is the term used by the SCSI Trade Association to describe Fast-40 SCSI, as documented in some versions of the SPI-2 draft standard.

It is the policy of Symbios Logic to improve products as new technology, components, software, and firmware become available. Symbios Logic, therefore, reserves the right to change specifications without notice.

The products in this manual are not intended for use in life-support appliances, devices, or systems. Use of these products in such applications without the written consent of the appropriate Symbios Logic officer is prohibited.

Copyright ©1995, 1996, 1997 By Symbios Logic Inc. All Rights Reserved Printed in U.S.A.

We use comments from our readers to improve Symbios product literature. Please e-mail any comments regarding technical documentation to pubs@symbios.com.

# **Purpose and Audience**

This manual provides basic information on the SYM53C8XX family of PCI-SCSI I/O Processors to software developers writing device drivers for SCSI devices that use these products. It describes basic chip operation and provides detailed information on the SCRIPTS programming language, a high-level interface for controlling Symbios Logic SCSI processors. The programming examples and instructions in this guide assume that the device driver is in "C" language. The examples are primarily written for PC-based architectures, but SCRIPTS-based drivers can run on any hardware platform. More detailed information on SCSI specifications can be found in the references listed in the section "Additional Information."

The diskette that accompanies this programming guide contains several "C" and SCRIPTS sample programs that implement many of the programming tasks discussed in this book. It also contains the NASM SCRIPTS assembler and the NVPCI SCRIPTS debugger. Please consult the "read me" file on the diskette for a list and description of all sample programs. For the most up-to-date versions of these and other sample programs, please contact the Symbios Logic electronic bulletin board.

# **Additional Information**

| ANSI SCSI-2 Standard,<br>SCSI-3 Parallel Interface<br>(SPI) Standard  | The SCSI-2 document is the final, approved standard for SCSI-2.<br>The SPI document is still in draft. Both of these documents can be<br>obtained from:<br>Global Engineering Documents<br>15 Inverness Way East<br>Englewood, CO 80112<br>(800)-854-7179 or (303) 792-2181 (outside U.S.)<br>Ask for document number X3.131-199X (SCSI-2) or X3.253 (SPI)                       |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCSI Bench Reference,<br>SCSI Encyclopedia                            | The SCSI Bench Reference is an applications-oriented guide to the<br>basics of SCSI. It is intended as a quick reference guide only. The<br>SCSI Encyclopedia is a multi-volume reference that describes all<br>SCSI-1 and SCSI-2 commands and protocols. It contains detailed<br>information on all topics covered. These and other reference<br>materials can be ordered from: |

|                                                                       | ENDL Publications<br>14426 Black Walnut Court<br>Saratoga, CA 95070<br>(408) 867-6642                                                                                                                                                                                                                                                                                            |

| What Is SCSI?<br>Understanding the Small<br>Computer System Interface | This easy-to-read book contains a high-level overview of how SCSI<br>works, based on the SCSI-1 standard. It is excellent for anyone with<br>no exposure to SCSI. It can be obtained from:<br>Prentice Hall<br>Englewood Cliffs, NJ 07632<br>(201) 767-5937<br>Ask for document number ISBN 0-13-796855-8                                                                        |

| Symbios Logic Electronic<br>Bulletin Board                            | This BBS provides updated information on Symbios Logic SCSI products, including sample SCRIPTS.<br>(719) 533-7235                                                                                                                                                                                                                                                                |

| SCSI Electronic Bulletin<br>Board                                     | Contact this BBS for general information on SCSI, including the<br>status of SCSI specifications, and electronic copies of draft<br>standards.<br>(719) 533-7950                                                                                                                                                                                                                 |

| Symbios Logic Internet<br>Anonymous FTP Site                          | This FTP site has general information similar to that on the electronic bulletin board. The address is: ftp.symbios.com (204.131.200.1) \pub\symchips\scsi.                                                                                                                                                                                                                      |

Symbios Logic World Wide Web Home Page The Symbios Logic home page has general information about our company and products. The address is http://www.symbios.com.

# **Revision Record**

| Page No. | Date | Remarks                                                                                                                                                      |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| all      | 8/96 | Version. 2.0                                                                                                                                                 |

|          | 6/97 | Version 2.1. Added information on<br>SYM53C885 and SYM53C876; added chapter<br>on programming multifunction controllers;<br>minor typographical corrections. |

# Contents

| i    |

|------|

| ii   |

| iv   |

| xiii |

| xvii |

|      |

### Chapter 1

## Introduction

| What is Covered in This Guide                | 1-1 |

|----------------------------------------------|-----|

| Product Overview                             | 1-2 |

| Benefits of Ultra SCSI and Ultra2 SCSI       | 1-5 |

| System Overview                              | 1-6 |

| How SCRIPTS Operations Control the SYM53C8XX | 1-7 |

| Conventions                                  | 1-8 |

### Chapter 2

### Programming the SYM53C8XX With SCRIPTS

| 0 0                                             |       |

|-------------------------------------------------|-------|

| The SCRIPTS Processor                           | 2-1   |

| SCRIPTS and the SCSI Bus Phases                 | 2-2   |

| Assembling SCSI SCRIPTS                         | 2-3   |

| Using SCSI SCRIPTS                              | 2-6   |

| SCRIPTS Data Sizes                              | 2-6   |

| SCSI SCRIPTS Language Elements                  | 2-7   |

| SCSI SCRIPTS Expressions                        | 2-7   |

| SCSI SCRIPTS Keywords                           | 2-8   |

| Description of SCRIPTS Instructions             |       |

| I/O Instructions                                | 2-8   |

| Memory Move Instructions                        | 2-9   |

| Transfer Control Instructions                   | 2-9   |

| Read/Write Instructions                         | 2-9   |

| Block Move Instructions                         | .2-10 |

| Load and Store Instructions                     | .2-10 |

| Big and Little Endian Byte Addressing           | .2-10 |

| Order of SCRIPTS Instructions                   | .2-11 |

| Operating Register Access from Firmware         | .2-11 |

| Operating Register Access from SCRIPTS Routines |       |

| User Data Byte Ordering                         | .2-11 |

| • •                                             |       |

| Chapter 3                                 |

|-------------------------------------------|

| The SYM53C8XX Instruction Set             |

| Overview                                  |

| CALL                                      |

| CHMOV                                     |

| CLEAR                                     |

| DISCONNECT                                |

| INT 3-13                                  |

| INTFLY                                    |

| JUMP                                      |

| LOAD                                      |

| MOVE 3-29                                 |

| MOVE MEMORY                               |

| MOVE REGISTER 3-34                        |

| NOP 3-38                                  |

| RESELECT 3-39                             |

| RETURN                                    |

| SELECT 3-45                               |

| SET 3-47                                  |

| STORE 3-49                                |

| WAIT DISCONNECT 3-51                      |

| WAIT RESELECT 3-52                        |

| WAIT SELECT 3-54                          |

| Instruction Examples 3-56                 |

| I/O Instruction Example 3-56              |

| Memory Move Instruction Example 3-57      |

| Transfer Control Instruction Example 3-59 |

| Read/Write Instruction Example 3-60       |

| Block Move Instruction Example 3-61       |

| Load/Store Instruction Example 3-62       |

# Chapter 4 Using the Symbios Logic Assembler

| Overview                                         | . 4-1 |

|--------------------------------------------------|-------|

| Starting NASM                                    | . 4-1 |

| Command Line Options                             | . 4-3 |

| A [arch] - Specify processor for code generation | . 4-3 |

| B - Binary Cross Reference Values                | . 4-3 |

| E - Creates an error listing file                | . 4-3 |

| L - Creates a listing file                       | . 4-4 |

| O - Generate output file                         | . 4-4 |

| P - Generate Partial "C" Source                  | . 4-4 |

| S - Generate .BIN Output                         | . 4-4 |

|                                                  |       |

| U - Omit Termination Record4-4     |

|------------------------------------|

| V - Verbose Messages4-4            |

| X - Patch Offsets4-4               |

| Example Assembler Command Lines4-5 |

| How NASM Parses SCRIPTS Files4-5   |

| Assembler Declarative Keywords4-6  |

| ABSOLUTE4-7                        |

| ARCH4-7                            |

| ENTRY4-8                           |

| EXTERN                             |

| PASS4-9                            |

| PROC                               |

| RELATIVE4-10                       |

| TABLE                              |

| Conditional Keywords               |

| If4-13                             |

| When4-13                           |

| Logical Keywords                   |

| NOT                                |

| AND                                |

| OR4-13                             |

| Flag Fields4-14                    |

| ACK4-14                            |

| ATN                                |

| TARGET                             |

| CARRY                              |

| Qualifier Keywords4-14             |

| DSAREL                             |

| FROM4-14                           |

| MASK                               |

| MEMORY                             |

| PTR                                |

| REG4-15                            |

| REL                                |

| ТО4-15                             |

| WITH                               |

| NOFLUSH                            |

| Other Keywords                     |

| Action Keywords4-16                |

| SCSI Phases                        |

| Register Names4-16                 |

| -                                  |

### Chapter 5 **The NASM Output File**

| Overview                  | 5-1  |

|---------------------------|------|

| NASM Output File Sections | 5-3  |

| SCRIPTS Array             | 5-3  |

| External                  | 5-6  |

| Relative                  | 5-7  |

| Entry                     | 5-9  |

| Label Patches             | 5-9  |

| Absolute                  | 5-10 |

| Termination Record        | 5-11 |

|                           |      |

#### Chapter 6

### Using the Registers to Control Chip Operations

| Overview                         |     |

|----------------------------------|-----|

| SCSI Registers                   | 6-1 |

| DMA Registers                    |     |

| SCRIPTS Registers                |     |

| Interrupt Registers              |     |

| Test and Miscellaneous Registers |     |

| General Purpose Registers        |     |

| Register Initialization          |     |

|                                  |     |

### Chapter 7

# Integrating SCRIPTS Programs Into "C" Language Drivers

| Overview                       | 7-1 |

|--------------------------------|-----|

| Initializing the SYM53C8XX7    | 7-1 |

| Table Indirect Operations    7 | 7-3 |

| Patching                       | 7-7 |

| EXTERN Buffers                 | 7-7 |

| RELATIVE Buffers               | 7-8 |

| ABSOLUTE Values                | 7-8 |

| Buffer Addresses 7             | 7-8 |

| Byte Counts                    | 7-9 |

| Absolute JUMP/CALL Addresses 7 |     |

| Entry Locations                | 7-9 |

| Self Modifying SCRIPTS Code 7  |     |

| Running a SCRIPTS Program7-    |     |

# Chapter 8 Writing Device Drivers With SCRIPTS

| Command Block.8-3Power Up Example.8-3I/O Request Process.8-4How to Write a Device Driver With SCRIPTS8-6Table Indirect Addressing.8-7Block Move Instructions.8-7Select/Reselect Instructions8-8Defining a Table8-10Relative Addressing.8-11                        | Overview                                  | 8-1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------|

| I/O Request Process       8-4         How to Write a Device Driver With SCRIPTS       8-6         Table Indirect Addressing       8-7         Block Move Instructions       8-7         Select/Reselect Instructions       8-8         Defining a Table       8-10 | Command Block                             | 8-3  |

| How to Write a Device Driver With SCRIPTS8-6Table Indirect Addressing8-7Block Move Instructions8-7Select/Reselect Instructions8-8Defining a Table8-10                                                                                                              | Power Up Example                          | 8-3  |

| Table Indirect Addressing8-7Block Move Instructions8-7Select/Reselect Instructions8-8Defining a Table8-10                                                                                                                                                          | I/O Request Process                       | 8-4  |

| Block Move Instructions                                                                                                                                                                                                                                            | How to Write a Device Driver With SCRIPTS | 8-6  |

| Select/Reselect Instructions                                                                                                                                                                                                                                       | Table Indirect Addressing                 | 8-7  |

| Defining a Table8-10                                                                                                                                                                                                                                               | Block Move Instructions                   | 8-7  |

|                                                                                                                                                                                                                                                                    | Select/Reselect Instructions              | 8-8  |

| Relative Addressing                                                                                                                                                                                                                                                | Defining a Table                          | 8-10 |

|                                                                                                                                                                                                                                                                    | Relative Addressing                       | 8-11 |

### Chapter 9

### **SCRIPTS Programming Topics**

| Overview                                             | 9-1  |

|------------------------------------------------------|------|

| Scatter/Gather Operations                            | 9-1  |

| Loopback Mode                                        | 9-4  |

| Loopback Example - Selection                         | 9-4  |

| Byte Recovery on Target Disconnect                   | 9-9  |

| Saving the State of the                              |      |

| SYM53C8XX                                            | 9-9  |

| Updating the SCRIPTS Program                         | 9-12 |

| Cleaning Up                                          |      |

| Example Byte Recovery Code                           | 9-12 |

| Synchronous Negotiation and Transfer                 | 9-18 |

| Interrupt Handling                                   | 9-19 |

| Polling and Hardware Interrupts                      | 9-19 |

| Registers                                            | 9-19 |

| Fatal vs. Non-Fatal Interrupts                       | 9-20 |

| Masking                                              | 9-21 |

| Stacked Interrupts                                   | 9-22 |

| Halting in an Orderly Fashion                        | 9-23 |

| Sample Interrupt Service Routine                     | 9-23 |

| Migrating Existing Software to Ultra and Ultra2 SCSI | 9-24 |

| Clock Divider Bits                                   | 9-25 |

| Ultra Enable Bit                                     | 9-25 |

| Loading the New Register Values                      | 9-25 |

| Negotiating Synchronous Transfers                    | 9-26 |

| Using the SCSI Clock Doubler                         | 9-26 |

| Using the SCSI                                       |      |

| Clock Quadrupler                                     |      |

| Using the SCRIPTS RAM                                |      |

| Loading SCRIPTS RAM                                  |      |

| Programming Techniques when Using SCRIPTS RAM        |      |

| Patching Internal and External SCRIPTS Programs      | 9-36 |

| Symbios Logic PCI-SCSI Programming Guide             | ix   |

### Chapter 10 Multi-Threaded I/O

| Overview                                   | 10-1 |

|--------------------------------------------|------|

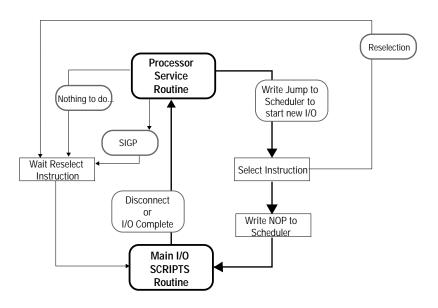

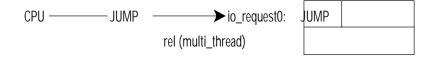

| Multi-threaded Operations Flow             | 10-2 |

| SCRIPTS Areas                              | 10-3 |

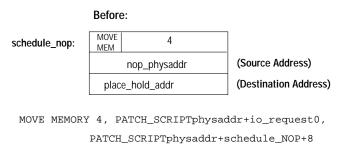

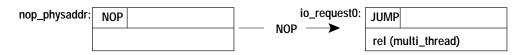

| Multi-Threaded SCRIPTS Example             | 10-3 |

| Using the SIGP bit to Abort an Instruction | 10-9 |

| I/O Completion1                            | 0-11 |

### Chapter 11

### **Programming Multifunction Devices**

| Using the SYM53C885 Power Management Feature | 11-1 |

|----------------------------------------------|------|

| Coma Mode                                    | 11-2 |

| Snooze Mode                                  | 11-2 |

| Register Bits Used for Power Management      | 11-2 |

| Programming the SYM53C885 Internal Arbiter   | 11-3 |

#### Chapter 12

### Using the SYM53C8XX in Target Applications

| Overview                                   | 2-1 |

|--------------------------------------------|-----|

| Registers Used for Target Operation 12     | 2-3 |

| Using SCRIPTS for Target Operations 12     | 2-4 |

| Sample Target Operation SCRIPTS Program    | 2-4 |

| Synchronous Negotiation by a Target Device | 17  |

#### Chapter 13

### **Debugging the SYM53C8XX**

| Overview                        | 13-1 |

|---------------------------------|------|

| Chip Debugging Guidelines       | 13-3 |

| Common Problems/Things to Check | 13-4 |

#### Appendix A NASM Error Messages

| 0            |      |

|--------------|------|

| Errors       | A-1  |

| Fatal Errors | A-15 |

| Warnings     | A-16 |

|              |      |

### Appendix B **Register Summaries**

| 0                     |             |      |

|-----------------------|-------------|------|

| SYM53C810A Operating  | g Registers | B-1  |

| SYM53C815 Operating I | Registers   | B-7  |

| SYM53C825A Operating  | g Registers | B-12 |

| SYM53C860 Operating I | Registers   | B-18 |

| SYM53C875 Operating I | Registers   | B-24 |

| SYM53C876 Operating I | Registers   | B-30 |

| SYM53C885 SCSI Regis  | ter Summary | B-36 |

| SYM53C895 Operating I | Registers   | B-42 |

|                       |             |      |

### Appendix C

### Multi-Threaded SCRIPTS Example

| Glossary | Glossary-1 |

|----------|------------|

| Index    | Index-1    |

Table of Contents

# List of Figures

#### Chapter 1 Introduction

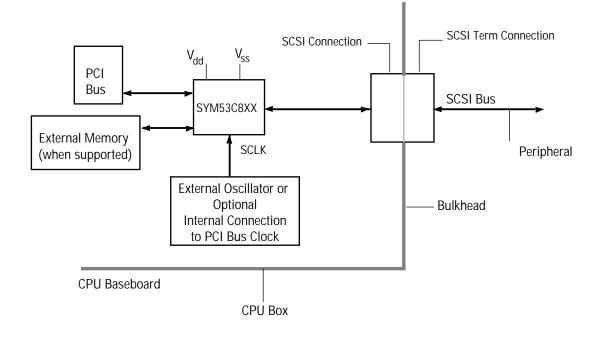

| Figure 1-1<br>SYM53C8XX Block Diagram   |

|-----------------------------------------|

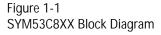

| Figure 1-2<br>Typical SCRIPTS Operation |

#### Chapter 2

### **Programming the SYM53C8XX With SCRIPTS**

| Figure 2-1              |      |      |     |

|-------------------------|------|------|-----|

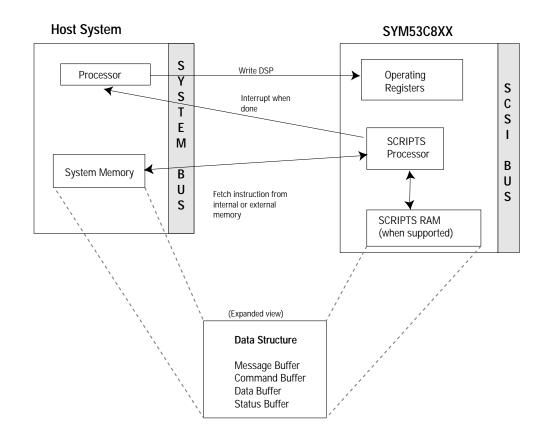

| Assembling SCSI SCRIPTS | <br> | <br> | 2-5 |

#### Chapter 3 The SYM53C8XX Instruction Set

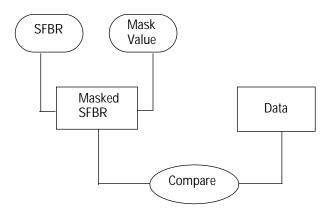

| Figure 3-1<br>Use of the Mask Keyword 3-5         |

|---------------------------------------------------|

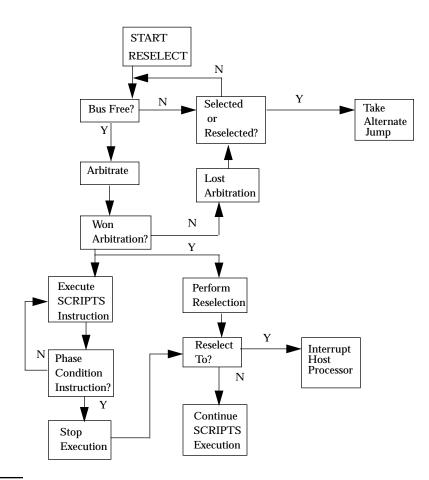

| Figure 3-2<br>Reselection Instruction             |

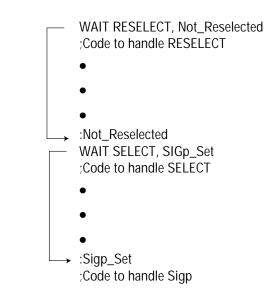

| Figure 3-3<br>WAIT RESELECT and the SIGP bit      |

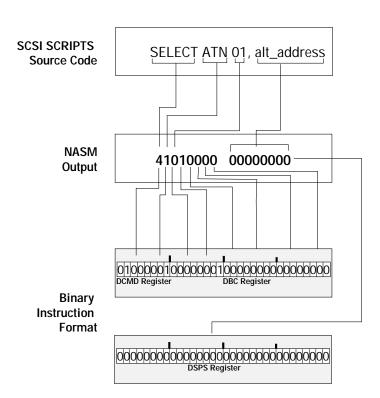

| Figure 3-4<br>I/O Instruction Type 3-57           |

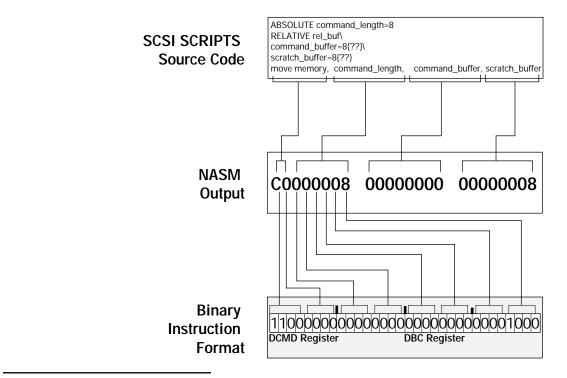

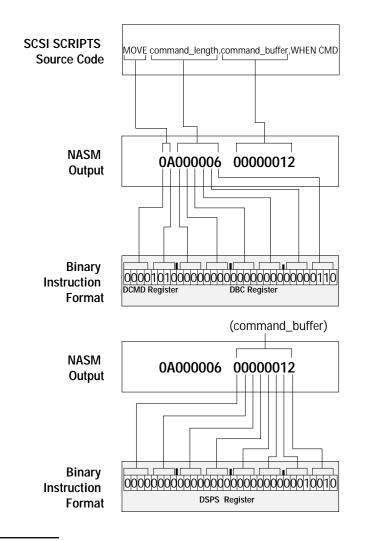

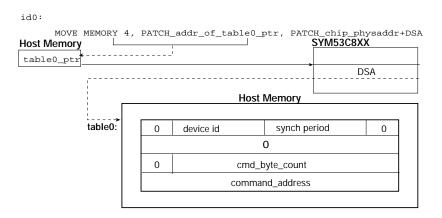

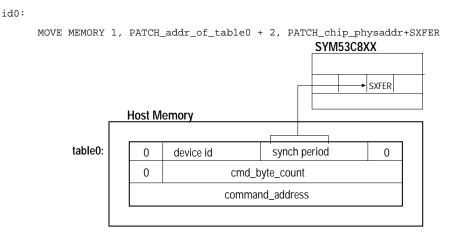

| Figure 3-5<br>Memory Move Instruction Part 1 3-58 |

| Figure 3-6<br>Memory Move Instruction Part 2 3-58 |

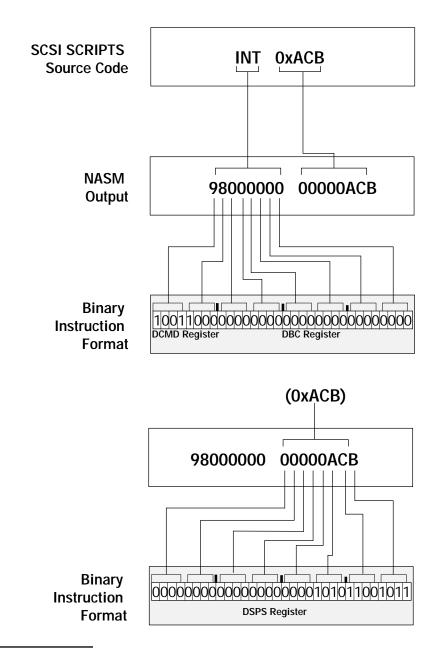

| Figure 3-7<br>Transfer Control Instruction 3-59   |

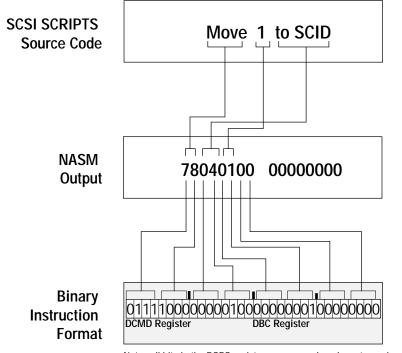

| Figure 3-8<br>Read/Write Instruction              |

| Figure 3-9<br>Block Move Instruction              |

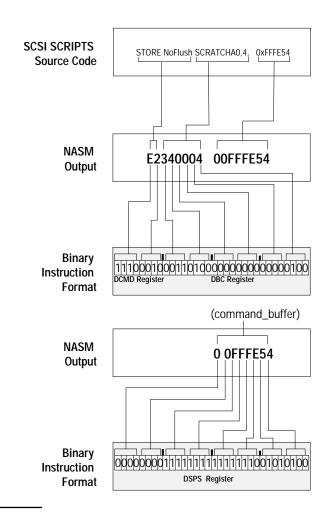

| Figure 3-10<br>Load/Store Instruction             |

# Chapter 5 The NASM Output File

| Figure 5-1                      |     |

|---------------------------------|-----|

| Structures in a SCRIPTS Program | 5-2 |

#### Chapter 7

### Integrating SCRIPTS Programs Into "C" Language Drivers

| Figure 7-1 SCRIPTS Source File | 7-12 |

|--------------------------------|------|

| Figure 7-2<br>NASM Output File | 7-16 |

#### Chapter 8 Writing Device Drivers With SCRIPTS

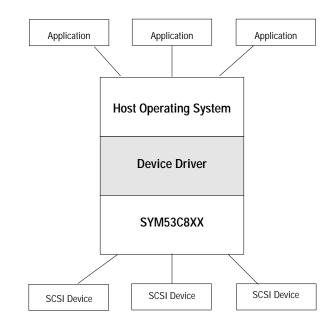

| Figure 8-1 The Role of the SCSI Device Driver    | -1 |

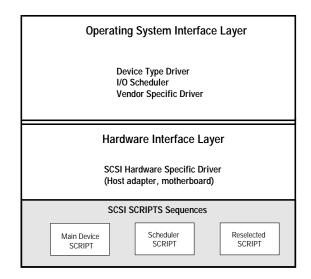

|--------------------------------------------------|----|

| Figure 8-2      SCSI Device Driver Layers      8 | -2 |

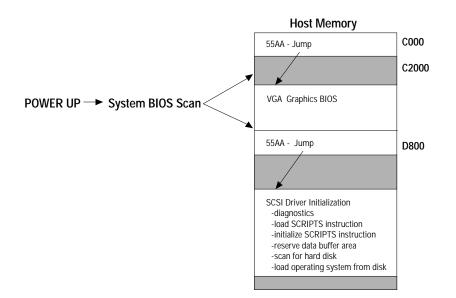

| Figure 8-3      Power Up Example      8          | -4 |

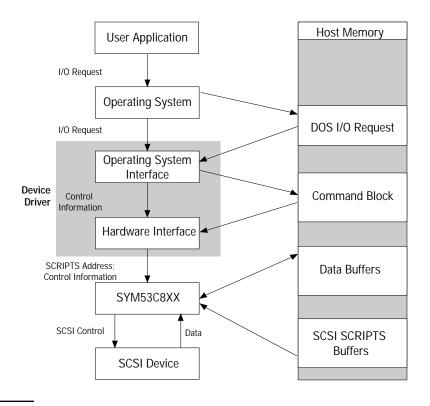

| Figure 8-4           I/O Operation         8     | -5 |

| Figure 8-5 Table Indirect Addressing             | -9 |

| Figure 8-6      Table Definition      8-1        | 10 |

#### Chapter 9 SCRIPTS Programming Topics

| Figure 9-1      Storing Data Structures in SCRIPTS RAM | 9-29 |

|--------------------------------------------------------|------|

| Figure 9-2<br>External Script (.LIS):                  | 9-31 |

| Figure 9-3<br>External Script (.OUT):                  | 9-32 |

| Figure 9-4                       |      |

|----------------------------------|------|

| Internal Script (.LIS):          | 9-33 |

| Figure 9-5                       |      |

| Internal SCRIPTS Program (.OUT): | 9-34 |

### Chapter 10 Multi-Threaded I/O

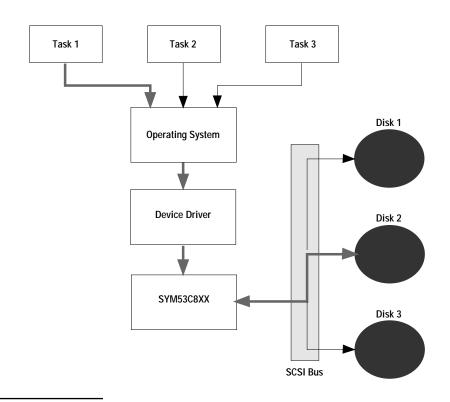

| Figure 10-1 Multi-threaded System Operation            | 10-1 |

|--------------------------------------------------------|------|

| Figure 10-2<br>Multi-threaded SCRIPTS Operational Flow | 10-3 |

List of Figures

# List of Tables

#### Chapter 1 Introduction

| Table 1-1         Features and Functions of SYM53C8XX Family Chips | 1-3 |

|--------------------------------------------------------------------|-----|

| Table 1-2         Conventions Used in This Programming Guide       | 1-9 |

#### Chapter 2 Programming the SYM53C8XX With SCRIPTS

| Table 2-1SCSI Protocol and SCRIPTS instructions2-2 |  |

|----------------------------------------------------|--|

| Table 2-2Big and Little Endian Byte Addressing     |  |

# Chapter 3 The SYM53C8XX Instruction Set

Table 3-1 SCRIPTS Instructions Supported by the SYM53C8XX Family. 3-1

#### Chapter 4 Using the Symbios Logic Assembler

| Table 4-2Code Generation Keywords                    |

|------------------------------------------------------|

| Table 4-3Miscellaneous Keywords4-6                   |

| Table 4-1      Data Definition and Storage Keywords. |

# Chapter 5 The NASM Output File

| Table 5-1                                      |     |

|------------------------------------------------|-----|

| Relationship Between Entry and PROC Statements |     |

| and Output File                                | 5-5 |

#### Chapter 6 Using the Registers to Control Chip Operations

| Table 6-1SYM53C8XX SCSI Registers6-2                              |

|-------------------------------------------------------------------|

| Table 6-2SYM53C8XX DMA Registers.6-4                              |

| Table 6-3SYM53C8XX SCRIPTS Registers6-5                           |

| Table 6-4SYM53C8XX Interrupt Registers6-6                         |

| Table 6-5SYM53C8XX Test Registers.6-7                             |

| Table 6-6      SYM53C8XX General Purpose Registers                |

| Table 6-7         53C815/53C810A/53C860 Startup Bits.             |

| Table 6-8         SYM53C825A/875/876/885/895         Startup Bits |

#### Chapter 7 Integrating SCRIPTS Programs Into "C" Language Drivers

#### Chapter 8 Writing Device Drivers With SCRIPTS

#### Chapter 9 SCRIPTS Programming Topics

#### Chapter 10 Multi-Threaded I/O

#### Chapter 11 Programming Multifunction Devices

| Table 11-1                             |     |

|----------------------------------------|-----|

| SYM53C885 Power Management Registers 1 | 1-3 |

### Chapter 12

# Using the SYM53C8XX in Target Applications

| Table 12-1         SCSI Protocol and Target SCRIPTS Instructions         12-1 |

|-------------------------------------------------------------------------------|

| Table 12-2                                                                    |

| Register Bits Used for Target Operation 12-3                                  |

# Chapter 13 **Debugging the SYM53C8XX**

Chapter A NASM Error Messages

Chapter B Register Summaries

Chapter C Multi-Threaded SCRIPTS Example

## Chapter 1

# Introduction

# What is Covered in This Guide

This manual provides basic information for writing device drivers that use the SYM53C810A, SYM53C815, SYM53C825A, SYM53C860, SYM53C875, and SYM53C895, SYM53C876, and the SCSI portion of the SYM53C885(this group of products is referred to as SYM53C8XX).

- This chapter introduces the SYM53C8XX features and functions, and the parts of the PCI-SCSI system that are involved in operating the chip.

- Chapter 2 describes the SCRIPTS processor and programming language in depth, including how SCRIPTS programs are integrated with "C" code to execute SCSI commands.

- Chapter 3 describes the SYM53C8XX instruction set, with detailed functional descriptions and usage guidelines for all of the instructions supported by the SYM53C8XX.

- Chapter 4 and Chapter 5 cover the Symbios Logic Assembler (NASM), including directives, and the .out file format.

- Chapter 6 contains functional and address information on the SYM53C8XX register set.

- Chapter 7 illustrates the relationship between the SCRIPTS program and the "C" language device driver.

- Chapter 8 and Chapter 9 address specific kinds of driver applications, with code samples for all applications discussed.

- Chapter 10 contains guidelines for writing SCRIPTS for multithreaded applications.

- Chapter 11 contains specific information for programming the Symbios Logic multifunction controllers SYM53CX885 and SYM53C876.

- Chapter 12 provides guidelines that are specific to using the SYM53C8XX in a target device.

- Chapter 13 provides information on debugging SCRIPTS programs.

- The appendixes contain a listing of NASM error messages, a glossary, a register summary, and a sample multi-threaded SCRIPTS program.

This manual is written for users who are familiar with the SCSI and PCI specifications, and have a working knowledge of computer architectures and programming. The Preface of this document identifies sources for obtaining some of this background information, if needed.

## **Product Overview**

The SYM53C8XX PCI-SCSI I/O Processor is based on the SYM53C7XX SCSI I/O Processor family architecture, with a host interface to the Peripheral Component Interconnect (PCI) bus.

The SYM53C8XX connects to the PCI bus without glue logic. The SYM53C810A and SYM53C860 are optimized for motherboard applications; a complete design can be implemented in less than four square inches of space on the motherboard. The SYM53C815, SYM53C825A, SYM53C875, and SYM53C895 are ideal for host adapter and motherboard applications, because of an added external memory interface which allows BIOS code to be placed in an external EEPROM to provide a bootable host adapter. The SYM53C825A, SYM53C875, and SYM53C895 have 4KB of onboard RAM for SCRIPTS instruction storage, to minimize PCI bus overhead by performing SCRIPTS instruction fetches without using the PCI bus. The SYM53C885 and SYM53C876 are multifunction controllers that each use only one PCI bus load. The SYM53C885 includes a SCSI I/O Processor and an Ethernet controller, and the SYM53C876 contains two independent SCSI functions.

The Symbios Logic SCSI I/O Processors are the first products to concentrate the functions of an intelligent SCSI adapter board onto a single chip. The SYM53C8XX integrates a high-performance SCSI core, a PCI bus master DMA core, and the SCSI SCRIPTS<sup>™</sup> processor to meet the flexibility requirements of SCSI-3 and future SCSI standards. It executes multi-threaded I/O algorithms with minimum host processor intervention, reducing the protocol overhead required for SCSI operations to as little as one interrupt per SCSI I/O. The SCRIPTS language, a high-level instruction set, provides complete programmability of I/O operations and supports the flexibility needed for multi-threaded I/O algorithms. The SYM53C8XX uses SCRIPTS to provide: phase sequencing without processor intervention; automatic bus arbitration; data or phase comparison for independent SCSI algorithm decisions; and DMA interface control. All SYM53C8XX family chips are also supported by Symbios Logic software for connecting SCSI devices, including BIOS support for Symbios Logic SCSI processors and drivers for most types of SCSI peripherals under the major operating systems.

All SYM53C8XX chips feature on chip single-ended drivers; synchronous and asynchronous transfer capabilities; and Symbios Logic TolerANT® driver and receiver technology, for single-ended signal integrity in any cabling environment. They support bus mastering, automatic selection/reselection time-outs, 32-bit memory addressing, a 32-bit data bus, and PCI bursting. The features and functions of individual chips in the SYM53C8XX family are summarized in Table 1-1.

Note: the SCSI portion of the SYM53C885 is functionally comparable to the SYM53C875. For specific information on the features and functions of the SYM53C885, refer to the SYM53C885 Data Manual. For specific information on programming the Ethernet function of the SYM53C885, refer to the Symbios Logic PCI-Ethernet Programming Guide.

Note: the SYM53C876 has two SCSI functions, each comparable to the SYM53C875. For specific information on the features and functions of the SYM53C876, refer to the SYM53C876 Data Manual.

#### Table 1-1 Features and Functions of SYM53C8XX Family Chips

|                                | SYM53C810A                     | SYM53C860                                            | SYM53C815                      | SYM53C825A,<br>SYM53C825AJ         | SYM53C875,<br>SYM53C875J,<br>SYM53C875JB,<br>SYM53C875N  | SYM53C895                                                 |

|--------------------------------|--------------------------------|------------------------------------------------------|--------------------------------|------------------------------------|----------------------------------------------------------|-----------------------------------------------------------|

| Max. Transfer<br>Rate          | 5 MB/s async.<br>10 MB/s sync. | 5 MB/s async.<br>20 MB/s<br>sync. (w/<br>Ultra SCSI) | 5 MB/s async.<br>10 MB/s sync. | 10 MB/s<br>async.<br>20 MB/s sync. | 10 MB/s<br>async.<br>40 MB/s<br>sync. (w/<br>Ultra SCSI) | 10 MB/s<br>async.<br>80 MB/s<br>sync. (w/<br>Ultra2 SCSI) |

| DMA FIFO Size<br>(bytes)       | 80                             | 80                                                   | 64                             | 88 or 536                          | 88 or 536                                                | 112 or 816                                                |

| Synchronous<br>Offset (levels) | 8                              | 8                                                    | 8                              | 16                                 | 16                                                       | 31                                                        |

| SCRIPTS RAM                    | no                             | no                                                   | no                             | yes                                | yes                                                      | yes                                                       |

| Differential SCSI              | no                             | no                                                   | no                             | yes                                | yes                                                      | LVD and<br>high voltage<br>differential                   |

| Wide SCSI                      | no                             | no                                                   | no                             | yes                                | yes                                                      | yes                                                       |

| External Memory<br>Interface   | no                             | no                                                   | yes                            | yes                                | yes                                                      | yes                                                       |

#### Table 1-1 (Continued) Features and Functions of SYM53C8XX Family Chips

| SYM53C810A    | SYM53C860                                            | SYM53C815                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SYM53C825A,<br>SYM53C825AJ                                                                                                                                                                                                                                                                                                       | SYM53C875,<br>SYM53C875J,<br>SYM53C875JB,<br>SYM53C875N                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SYM53C895                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| yes           | yes                                                  | no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | yes                                                                                                                                                                                                                                                                                                                              | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| yes           | yes                                                  | no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | yes                                                                                                                                                                                                                                                                                                                              | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| no            | no                                                   | no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | yes                                                                                                                                                                                                                                                                                                                              | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| yes           | yes                                                  | no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | yes                                                                                                                                                                                                                                                                                                                              | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 2             | 2                                                    | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                                                                                                                                                                                                                                                                                                                               | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| yes           | yes                                                  | no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | yes                                                                                                                                                                                                                                                                                                                              | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| yes           | yes                                                  | no                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | yes                                                                                                                                                                                                                                                                                                                              | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Little Endian | Little Endian                                        | Big or Little<br>Endian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Big or Little<br>Endian<br>(except<br>53C825AJ)                                                                                                                                                                                                                                                                                  | Big or Little<br>Endian<br>(except<br>53C875J,<br>53C875JB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Big or Little<br>Endian                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 100 PQFP      | 100 PQFP                                             | 128 PQFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 160 PQFP                                                                                                                                                                                                                                                                                                                         | 160 PQFP,<br>169 BGA,<br>208 PQFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 208 PQFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |